基于CPLD的FPGA从并快速加载方案

时间:03-02

来源:电子技术设计

点击:

要3.8 s,FPGA加载时间过长,则会影响系统的启动时间。

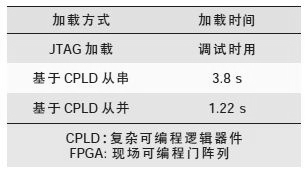

表2 是常用加载方式加载6SLX150T 型号FPGA 芯片数据所需时间比较。

表2 FPGA 加载时间对比

从上述分析可以得出结论,如果提高CPU 的局部总线写速度,加载FPGA 的时间就会更快。

5 结束语

使用基于CPLD 的FPGA 从并加载方案,相对于其它几种加载方式,虽然加载管脚增多,但加载时间大大缩短,并且如果提高CPU 局部总线的写速度,加载速度有进一步提高空间,满足通信系统快速启动的要求,具有很高的实用价值。

- Xilinx Kintex UltraScale 一半尺寸的 PCI Express 平台 (HTG-K816)(06-15)

- Xilinx全新参考设计提供业界首个单芯片400G解决方案(02-12)

- Xilinx用于工业自动化的机器视觉解决方案(11-30)

- Xilinx多协议机器视觉摄像机参考设计(12-01)

- 机器视觉技术原理解析及解决方案集锦(02-06)

- 机器视觉在汽车电子方向的应用解决方案(02-13)