开关电源电路开发设计秘籍大全

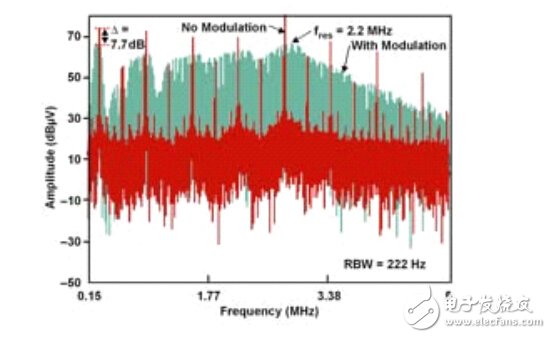

图8.3对有频率调制和无频率调制的EMI性能测量值进行了对比。此时的调制指数为4,正如我们预料的那样,基频下EMI性能大约降低了8dB。其他方面也很重要。

谐波被抹入 (smear into) 同其编号相对应的频带中,即第三谐波延展至基频的三倍。 这种情况会在一些较高频率下重复, 从而使噪声底限大大高于固定频率的情况。因此, 这种方法可能并不适用于低噪声系统。 但是, 通过增加设计裕度和最小化EMI

滤波器成本,许多系统都已受益于这种方法。

图8.3 改变电源频率降低了基频但提高了噪声底限

秘笈九 估算表面贴装半导体的温升

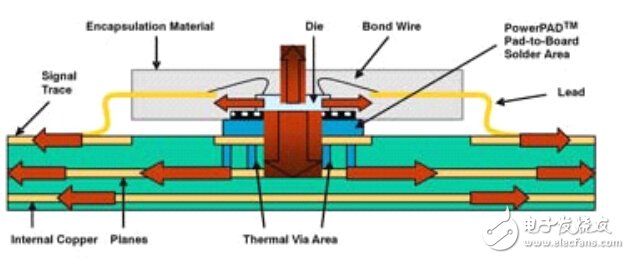

过去估算半导体温升十分简单。您只需计算出组件的功耗,然后采用冷却电路电模拟即可确定所需散热片的类型。现在出于对尺寸和成本因素的考虑,人们渴望能够去除散热片,这就使得这一问题复杂化了。贴装在散热增强型封装中的半导体要求电路板能够起到散热片的作用,并提供所有必需的冷却功能。如图9.1所示, 热量经过一块金属贴装片和封装流入印刷线路板 (PWB)。然后,热量由侧面流经PWB线迹,并通过自然对流经电路板表面扩散到周围的环境中。影响裸片温升的重要因素是PWB中的铜含量以及用于对流导热的表面面积。

图9.1 热量由侧面流经PWB线迹,然后从 PWB 表面扩散至周围环境

半导体产品说明书通常会列出某种PWB结构下结点至周围环境的热阻。这就是说,设计人员只需将这种热阻乘以功耗,便可计算出温升情况。但是,如果设计并没有具体的结构,或者如果需要进一步降低热阻,那么就会出现许多问题。

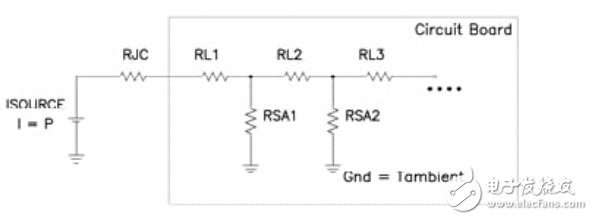

图9.2所示为热流问题的简化电模拟, 我们可据此深入分析。 IC电源由电流源表示,而热阻则由电阻表示。在各电压下对该电路求解,其提供了对温度的模拟。从结点至贴装面存在热阻,同时遍布于电路板的横向电阻和电路板表面至周围环境的电阻共同形成一个梯形网络。这种模型假设1)电路板为垂直安装,2)无强制对流或辐射制冷,所有热流均出现在电路板的铜中,3)在电路板两侧几乎没有温差。

图9.2 热流电气等效简化了温升估算

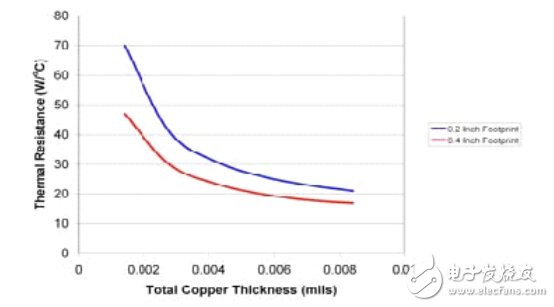

图9.3所示为增加PWB中的铜含量对提高热阻的影响。将 1.4 mils铜(双面,半盎司) 增加到8.4 mils( 4层 ,1.5盎司) , 就有可能将热阻提高3倍。 图中两条曲线:一条表示热流进入电路板、 直径为0.2英寸的小尺寸封装; 另一条表示热流进入电路板、 直径为0.4英寸的大尺寸封装。 这两条曲线均适用于9平方英寸的PWB。 这两条曲线均同标称数据紧密相关,同时都有助于估算改变产品说明书电路板结构所产生的影响。但是使用这一数据时需要多加谨慎,其假设9平方英寸PWB内没有其他功耗,而实际上并非如此。

图9.3 热流电气等效简化了温升估算

秘笈十 轻松估计负载瞬态响应

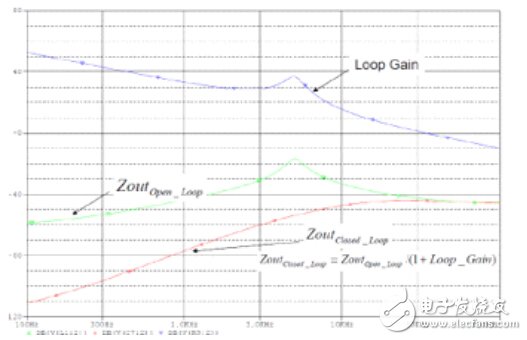

本篇电源设计小贴士介绍了一种通过了解控制带宽和输出滤波器电容特性估算电源瞬态响应的简单方法。该方法充分利用了这样一个事实,即所有电路的闭环输出阻抗均为开环输出阻抗除以 1 加环路增益,或简单表述为:

图10.1以图形方式说明了上述关系,两种阻抗均以dB-Ω或20*log [Z]为单位。在开环曲线上的低频率区域内,输出阻抗取决于输出电感阻抗和电感。当输出电容和电感发生谐振时,形成峰值。高频阻抗取决于电容输出滤波器特性、等效串联电阻 (ESR) 以及等效串联电感 (ESL)。将开环阻抗除以1加环路增益即可计算得出闭环输出阻抗。

由于该图形以对数表示,即简单的减法,因此在增益较高的低频率区域阻抗会大大降低;在增益较少的高频率区域闭环和开环阻抗基本上是一样的。在此需要说明如下要点:1)峰值环路阻抗出现在电源交叉频率附近,或出现在环路增益等于1(或0dB) 的地方; 以及2) 在大部分时间里, 电源控制带宽都将会高于滤波器谐振,因此峰值闭环阻抗将取决于交叉频率时的输出电容阻抗。

图10.1闭环输出阻抗峰值Zout出现在控制环路交叉频率处

一旦知道了峰值输出阻抗,就可通过负载变动幅度与峰值闭环阻抗的乘积来轻松估算瞬态响应。有几点注意事项需要说明一下,由于低相位裕度会引起峰化,因此实际的峰值可能会更高些。 然而, 就快速估计而言, 这种影响可以忽略不计 [1] 。第二个需要注意的事项与负载变化幅度上升有关。如果负载变化幅度变化缓慢较低),则响应取决于与上升时间有关的低频率区域闭环输出阻抗;如果负载变化幅度变化极为快速, 则输出阻抗将取决于输出滤波器ESL。 如果确实如此, 则可能需要更多的高

- EMI噪声分析及EMI滤波器的设计(10-07)

- 开关电源的EMC设计(09-15)

- 多层线路板在开关电源电路中应用(11-07)

- 双激式开关电源变压器存在的风险(01-20)

- 开关电源的分类及应用(02-17)

- 开关电源控制环路如何设计(04-11)