基于FPGA的USB3.0 HUB设计方案

USB总线是目前最为成功,应用最为广泛的外设接口。随着时代的进步和发展,电子产品、手持设备、超大容量的高清视频设备以及千万像素的数码相机等设备的需求越来越高,USB接口规范也需要相应地进行不断地更新和升级。USB3.0的最高理论速度达到了5Gbit/s,向需要更大电力支持的设备提供更好的支持和电力供应,它在USB2.0的基础上增加了新的电源管理功能,采用全双工数据通信,提供更快的传输速度,并且向下兼容USB2.0和USB1.1设备。USB体系主要包括三个部分:主机,设备和物理连接。主机通常是PC或者主机控制器;设备是指常用的U盘、带USB的摄像头、相机等设备;物理连接就是通常用的传输线,在USB3.0系统中,采用了对偶单纯形四线制差分信号线,因此可以支持双向并发数据流传输,这也是USB3.0相比于USB2.0设备速度提升的关键因素。

HUB是USB系统中的重要组成部分,且能够应用在大多数操作系统,它是建立主机与USB设备之间的桥梁。作为一类特殊的USB设备,可以同时将一个接口转换为多个接口,为用户提供了效率和便捷。

1. USB3.0 HUB的简介

1.1 USB3.0 HUB的基本组成

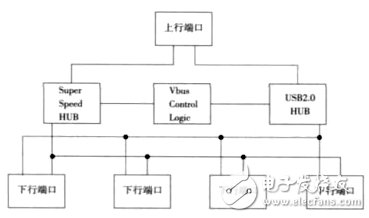

根据最新USB3.0的协议规定,USB3.0 HUB主要由Super Speed HUB,Vbus ControlLogic,USB2.0 HUB以及上下行端口组成。由于USB3.0是向下兼容的,所以它有完整的USB2.0 HUB设计,而Super Speed HUB部分就是USB3.0 HUB区别于USB2.0 HUB的主要部分。USB3.0 HUB基本结构如图1所示。

图1 USB3.0 HUB的基本结构

1.2 USB3.0集线器的功能

USB3.0 HUB是USB系统中的重要部分,它的基本功能如下:

1)基本连接功能。

2)电源管理功能。USB3.0能够提供900mA的电源,这样就可以给那些连接USB3.0的设备更快更好地完成充电。由于新的接口提供了额外的两条线,900mA的电力支持能够驱动无线适配器,这样在900mA的高电力支持下可以摆脱靠线缆连接的必要性。在大量数据传输的同时,空闲的设备可以自动进入低功耗状态,给正在传输的设备提供更好更快的性能支持。

3)设备连接和断开检测。

4)总线的错误检测和恢复。

5)HUB3.0的自动挂起和恢复功能。

6)向下兼容,下行端口同时支持高/低/全速设备。

2. Super Speed HUB的设计

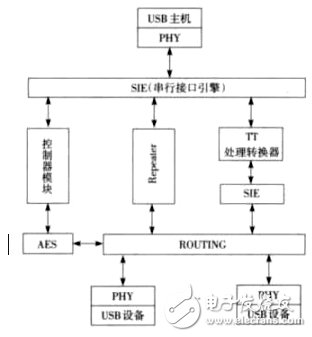

USB3.0 HUB是一种便携的低成本的USB3.0扩展接口,它的下行端口面向USB设备,上行端口面向PC主机或者嵌入式主机控制器,速度由上行端口的主机来决定,同时它在下行端口给设备提供连接和断开的检测,根据USB3.0最新协议规范,要实现上节所述各项功能设计。Super Speed HUB的整体构架如图2所示,包括SIE、控制、处理转换、中继、路由、AES加解密等部分。

图2 USB3.0 HUB的整体构架

2.1 SIE(Serial Interface Engine)模块

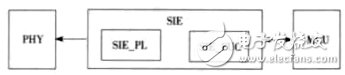

Super Speed HUB中的SIE模块处理USB规范中物理层和协议层的协议解析,它主要实现包的识别与产生、比特填充和提取、时钟与数据分离、NRZI编码和解码、PID(包标识符)的产生和检测、CRC校验码的识别和产生、地址检测等。SIE模块设计中,分为SIE_PL和SIE_FUC两个部分。SIE_PL模块负责数据包的解析与组织,PID(包标识符)产生与检测、CRC校验识别与产生、地址检测等。SIE_FUC模块主要实现SIE模块与MCU的接口逻辑功能。另外,为了使本系统设计更加稳定,SIE模块中采用跨时钟域的设计,一个是本地的48MHz的全局时钟,另外一个是USB主机从接收到的数据流中采样接收的12MHz数据时钟(即将48MHz本地全局时钟4分频得到)。SIE模块设计框图如图3所示。

图3 SIE模块设计框图

2.2 HUB控制器模块

HUB控制器主要完成HUB的管理及控制,实现与主机的交互。主机端通过类请求与HUB控制器模块通信,取得HUB端口的描述符,并且完成USB HUB及其下行端口的管理和控制。主机通过向端点0发送类请求和标准请求来实现HUB的枚举过程。

2.3 AES模块

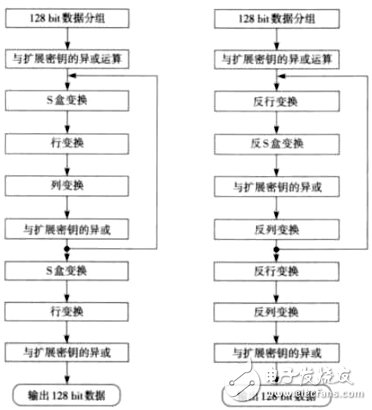

AES是一种基于置换和代替的算法,它实现加解密功能。在USB3.0 Super Speed模式下,根据用户的需求,当数据从上行端口向下行端口传输时,对数据进行加密,以防止信息窃取。同样,在数据由下行端口向上行端口传输时实现其解密过程。AES算法加解密过程如图4所示。

图4 AES算法加解密过程

在加解密的过程中,由于USB3.0 HUB的传输速度可达到3200Mbit/s,但是AES的加解密IP在250MHz的吞吐率下最高速率只能达到2400Mbit/s,因此在加解密的过程中需要2个AES来实现其功能。图5是USB3.0 AES加密原理图,从图中可以看到上行端口会向EM_A发送奇数128bit数据,向EM_B发送偶数128bit数据,同时,Mem_buf

- 十大智能家居产品(上)飞利浦Hub、Nest在列(11-05)

- 一种具有高可靠性的485 Hub星型总线(11-12)

- DIY不死 USB3.0/2.0存储硬盘综合大评测(02-24)

- 嵌入式应用的USB3.0 链路共享(07-04)

- 基于CYUSB3014的高速实时数据采集系统(02-26)

- USB3.0技术规格与信号完整性解析(07-05)