常见的五大ARM存储器之一:协处理器CP15

ARM存储系统有非常灵活的体系结构,可以适应不同的嵌入式应用系统的需要。ARM存储器系统可以使用简单的平板式地址映射机制(就像一些简单的单片机一样,地址空间的分配方式是固定的,系统中各部分都使用物理地址),也可以使用其他技术提供功能更为强大的存储系统。比如:

· 系统可能提供多种类型的存储器件,如FLASH、ROM、SRAM等;

· Caches技术;

· 写缓存技术(write buffers);

· 虚拟内存和I/O地址映射技术。

大多数的系统通过下面的方法之一实现对复杂存储系统的管理。

· 使能Cache,缩小处理器和存储系统速度差别,从而提高系统的整体性能。

· 使用内存映射技术实现虚拟空间到物理空间的映射。这种映射机制对嵌入式系统非常重要。通常嵌入式系统程序存放在ROM/FLASH中,这样系统断电后程序能够得到保存。但是通常ROM/FLASH与SDRAM相比,速度慢很多,而且基于ARM的嵌入式系统中通常把异常中断向量表放在RAM中。利用内存映射机制可以满足这种需要。在系统加电时,将ROM/FLASH映射为地址0,这样可以进行一些初始化处理;当这些初始化处理完成后将SDRAM映射为地址0,并把系统程序加载到SDRAM中运行,这样很好地满足嵌入式系统的需要。

· 引入存储保护机制,增强系统的安全性。

· 引入一些机制保证将I/O操作映射成内存操作后,各种I/O操作能够得到正确的结果。在简单存储系统中,不存在这样问题。而当系统引入了Cache和write buffer后,就需要一些特别的措施。

在ARM系统中,要实现对存储系统的管理通常是使用协处理器CP15,它通常也被称为系统控制协处理器(System Control Coprocessor)。

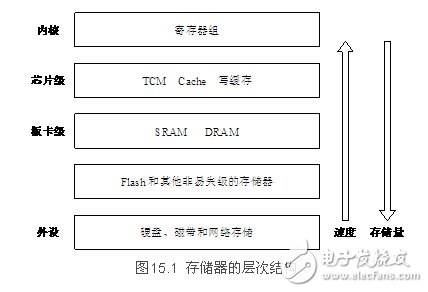

ARM的存储器系统是由多级构成的,每级都有特定的容量和速度。

图1显示了存储器的层次结构。

① 寄存器。处理器寄存器组可看作是存储器层次的顶层。这些寄存器被集成在处理器内核中,在系统中提供最快的存储器访问。典型的ARM处理器有多个32位寄存器,其访问时间为ns量级。

图1 存储器的层次结构

② 紧耦合存储器TCM。为弥补Cache访问的不确定性增加的存储器。TCM是一种快速SDRAM,它紧挨内核,并且保证取指和数据操作的时钟周期数,这一点对一些要求确定行为的实时算法是很重要的。TCM位于存储器地址映射中,可作为快速存储器来访问。

③ 片上Cache存储器的容量在8KB~32KB之间,访问时间大约为10ns。

④ 高性能的ARM结构中,可能存在第二级片外Cache,容量为几百KB,访问时间为几十ns。

⑤ DRAM。主存储器可能是几MB到几十MB的动态存储器,访问时间大约为100ns。

⑥ 后援存储器,通常是硬盘,可能从几百MB到几个GB,访问时间为几十ms。

注意TCM和SRAM在技术上相同,但在结构排列上不同;TCM在片上,而SRAM在板上。

协处理器CP15

ARM处理器支持16个协处理器。在程序执行过程中,每个协处理器忽略属于ARM处理器和其他协处理器的指令。当一个协处理器硬件不能执行属于它的协处理器指令时,将产生一个未定义指令异常中断,在该异常中断处理程序中,可以通过软件模拟该硬件操作。比如,如果系统不包含向量浮点运算器,则可以选择浮点运算软件模拟包来支持向量浮点运算。

CP15,即通常所说的系统控制协处理器(System Control Coprocesssor)。它负责完成大部分的存储系统管理。除了CP15外,在具体的各种存储管理机制中可能还会用到其他的一些技术,如在MMU中除CP15外,还使用了页表技术等。

在一些没有标准存储管理的系统中,CP15是不存在的。在这种情况下,针对协处理器CP15的操作指令将被视为未定义指令,指令的执行结果不可预知。

CP15包含16个32位寄存器,其编号为0~15。实际上对于某些编号的寄存器可能对应多个物理寄存器,在指令中指定特定的标志位来区分这些物理寄存器。这种机制有些类似于ARM中的寄存器,当处于不同的处理器模式时,某些相同编号的寄存器对应于不同的物理寄存器。

CP15中的寄存器可能是只读的,也可能是只写的,还有一些是可读可写的。在对协处理器寄存器进行操作时,需要注意以下几个问题。

· 寄存器的访问类型(只读/只写/可读可写)。

· 不同的访问引发的不同功能。

· 相同编号的寄存器是否对应不同的物理寄存器。

· 寄存器的具体作用。

CP15寄存器访问指令

通常对协处理器CP15的访问使用以下两种指令。

MCR:将ARM寄存器的值写入CP15寄存器中;

MRC:将CP15寄存

- 下一代Flash存储器在工业控制领域技术与应用(02-05)

- 闪迪瞄准汽车与工业领域 推出相应存储解决方案(04-04)

- 攻克可穿戴医疗存储器件封装难题(09-23)

- FPGA中SPI Flash存储器的复用编程方法的实现(09-13)

- 为何电子式电能表需要使用铁电存储器(F-RAM)(09-11)

- 铁电存储器的技术特点分析(09-18)