专用SOC安全控制架构的研究与设计

。与层次跳转进入ST9不同的是,通过调用2层代码来完成其相应功能时,在2层代码执行完毕后,芯片系统可以返回到ST6。而通过层次跳转命令进入 ST9时,完成规定的功能后,芯片系统保持在ST9,或者通过系统复位返回ST3,不允许其返回ST6。

1.2 状态位与控制参数设置

为实现上述各状态之间的正常跳转,芯片系统需要设置相应的状态位与控制参数,以寄存芯片运行时的控制信息和工作状态。状态位与控制参数设置是芯片安全体系结构建立的基础,基于芯片的权限状态划分,参照TPM与ATMELSC系列安全芯片对状态位与控制参数的配置,将LEVEL0作为专用SoC芯片状态位与控制参数的存储区,其具体设置如表1所列。

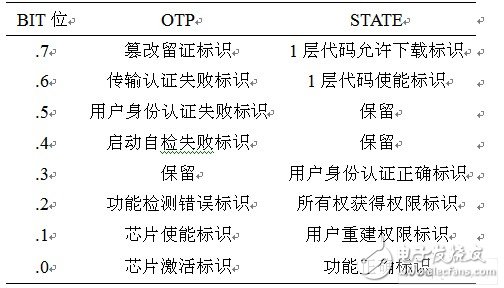

表1 LEVEL0状态位与控制参数配置表

在表1中,OTP(One Time Programmer)区是一次性编程区,用于芯片一次性设置的权限标识与状态留证。STATE为系统状态标识,用于标识芯片当前的权限状态信息。OTP 与STATE中各位的作用与位的对应关系如表2所示,其中各位均为高电平有效。

表2 OTP与STATE中状态位功能表

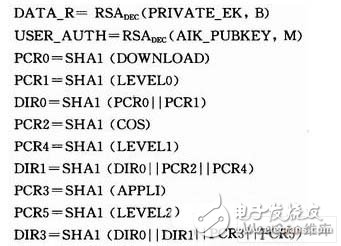

M_AUTH为制造商与开发商的共享秘密,M_PUBKEY为制造商公钥,SN为产品序列号,它们共同用于芯片的传输过程安全认证。 EK(Endors- ement Key)为芯片系统的身份认证密钥对,在实际应用过程中,芯片通过调用EK私钥对数据进行签名,以表明自身的合法身份。AIK(Attes-tation Identity Key)为开发商身份认证密钥对,在用户身份创建过程中由片内随机数与RSA算法IP核生成,用于用户的身份认证。PCR(Pla-tform. Configuration Register)是平台配置完整性寄存区。为满足专用SoC芯片在进行FPGA测试时对芯片系统的硬件规模限制,暂时为芯片系统配置了8个PCR,每个 PCR寄存器为20个字节。除PCR6和PCR7外,其余各PCR寄存器存储信息的表达式如下所示。

PCR0 = SHA1(DOWNLOAD)

PCR1 = SHA1(LEVEL0)

PCR2 = SHA1(COS)

PCR3 = SHA1(APPLI)

PCR4 = SHA1(LEVEL1)

PCR5 = SHA1(LEVEL2)

DIR(Data Integrity Register)是芯片系统的数据完整性寄存器,寄存芯片内部数据与代码的完整性信息,具体设计时,为芯片系统配置了3个DIR,分别存储三个层次的数据与代码的完整性,各DIR寄存器存储信息的表达式如下。

DIR0 = SHA1(PCR0||PCR1)

DIR1 = SHA1(DIR1||PCR2||PCR4)

DIR2 = SHA1(DIR1||DIR2||PCR3||PCR5)

USER_AUTH为用户与芯片系统的共享认证秘密,在用户创建时通过相应命令输入,完成用户的身份合法性验证。ERROR_SIG为认证错误次数寄存器,用于芯片系统对字典攻击的防护。ATTACK_EVI是攻击留证寄存器,对芯片系统所遭受的物理攻击次数与方式进行寄存。

2 芯片工作流程分析

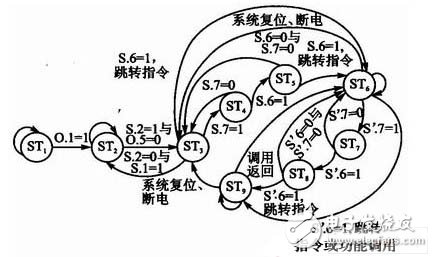

专用SoC芯片在其整个生命周期中,总处于某种特定的安全状态。基于芯片运行时的安全策略,结合状态位与控制参数设置,专用SoC芯片的状态转移流程如图1所示。

图1 芯片状态转移流程图

在上图中,S.n表示STATE的第n位,S’.n表示STATE’的第n位(位于LEVEL1中),0.n表示0TP的第n位。高电平表示对应条件成立,低电平表示对应条件不成立。

2.1 状态转移约束条件

专用SoC芯片按照其工作流程共有16种不同的状态转移路径,限于篇幅在此只介绍其中的一种状态转移路径。为简化书写记A=TDESENC(KEY_TDES,DATA_T),B=RSAENC(PUB EK,DATA R)。

当专用SoC芯片从ST3状态通过ST6状态转移到ST9状态时,应满足如下约束条件:

在正常启动时,芯片系统由ST3经过上电白检,完成对1层代码与数据、2层代码与数据的完整性验证。置位STATE.6,通过层次跳转命令,进入ST6,进而在ST6下,通过判断STATE’.6是否有效,决定可否进入ST9。在ST6下,也可通过功能调用命令进入ST9,执行部分2层代码的功能,并在执行完成后,正确返回到ST6。

2.2 专用SoC芯片的工作流程

①在开发商初次获得芯片后,系统处于初始状态ST1。加电后,系统首先对自身O层代码和数据区进行完整性检验,调用各功能模块IP核进行自检,若白检正确,则芯片可继续完成传输过程安全认证命令的接收与执行,否则置位OTP.4,芯片系统进入锁死状态,不提供任何功能服务。

②当OTP.1=0时,芯片系统仅允许传输过程安全认证命令的输入与执行。开发商通过传输安全认证命令,在允许的认证次数范围内,对芯片的真实性进行认证。若认证正确,芯片由初始状态ST1转移至使能状态ST2,并置位芯片使能标识OTP.1,等待用户创建命令的输入。若芯片真实性认证错误,芯片系

- Tensilica助力海信数字电视SOC芯片达业界最优(09-12)

- UltraSoC扩大规模以抓住嵌入式分析市场机遇(08-29)

- 嵌入式系统在电源设计中的运用(09-20)

- 基于4G通信的嵌入式数据通信系统设计(10-10)

- 汽车安全性能亟待升级 嵌入式系统把关护航(05-07)

- USB端口找到新居,落户嵌入式系统(02-11)