PDP显示器电源管理架构分析

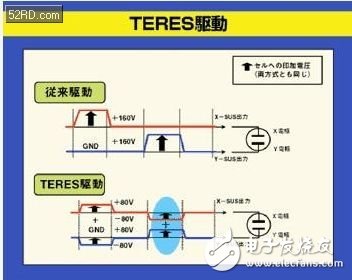

至于第二项,电压准位类型过多、电路过于复杂,多是指PDP的 Y极电路,Y极以分时多工方式饰演两角,此时Y极要与X极一同执行放电驱动,彼时Y极又要与Z极一同执行扫描驱动(显示画面的资料刷新、更新),在放电时 Y极需要使用-170V、-70V两种电压,在扫描时Y极则需要0V(接地)、+160V的电压,等于需要四种电压准位。

Y极使用的电压类型过多,运作电路上也过度复杂,使PDP电路成本居高,然TERES技术也对此进行改善,将运用的电压减至三种:+80V、0V、-80V,扫描时使用 0V、-80V,放电时使用0V、+80V,再加上扫描顺序的改变,如此可有效简化整体电路,使Y极电路所需的功能模组从五个减至三个,进而降低成本。

结论与建议

最后,必须瞭解:PDP的整体系统电路,包括显示驱动、显示控制、用电管理、保护电路等,现阶段都是与PDP原制造厂高度相依的,即便有PDP驱动、控制的应用晶片,也多是由原厂自行研制,并搭配原厂自有的设计而用,除原厂外的PDP电路设计多要高度倚赖自行的客制化设计心力,不易找到可倚赖的应用晶片。

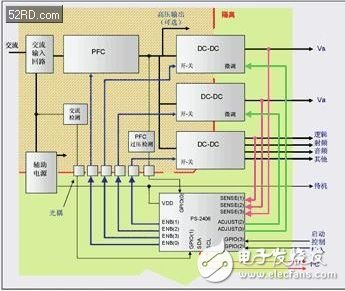

不过,PDP整体电路中仍有些部份可直接沿用较具弹性的可组态、可程式化晶片,在电源部份可使用具弹性调设组态的电源管理晶片,以此来因应PDP所需的多种电压准位,如Potentia Semiconductor的PS-2406晶片(具电源供应、调整、管理、保护等多重效用)即可用于PDP的电源电路设计中。又如Xilinx的 CPLD、FPGA亦可运用在PDP的逻辑电路设计中。

除这些外,PDP系统中的驱动电路、扫描电路、放电电路等,都还是要倚赖大比重的客制设计,且需要依据面板规格、特性表现来设计。

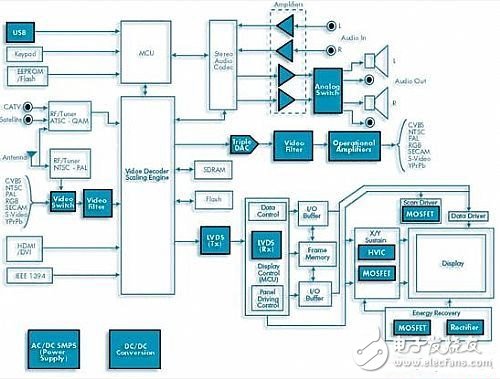

图一 Fairchild(快捷半导体)在PDP电路系统中所能提供的组件方案图(深色部位)。

图二 PDP显示原理图(剖面结构的观看角度)。

图三 PDP系统电路的主要功能区块图。

图四 富士通日立提出所谓的TERES技术,可让PDP的用电减少一半,电路成本也减半,图为TERES技术示意图。

图五 Potentia半导体的电源管理晶片:PS-2406

- OLED与PDP等离子技术的优缺点比较(06-11)

- LCD液晶拼接与DLP背投及PDP等离子技术对比(06-13)

- 等离子彩电微控制电路原理分析(06-14)

- 彩色PDP显示系统的驱动集成电路(06-14)

- 四大主流大屏显示技术对比分析(06-15)

- 等离子电视的技术指标以及优点详解(06-14)