彩色TFT液晶显示控制电路设计及其ASIC实现

色顺序寄存器相一致。例如,使用280×220型号的液晶显示器,在V_DIR=0(从上到下扫描)和H_DIR=1 (从左到右扫描)时奇数行的颜色顺序是RGB,偶数行颜色顺序为GBR,所以在设置起始行寄存器和起始列寄存器时一定要保证这样的颜色顺序,才能正确显示。

脉冲参数寄存器设置了各驱动脉冲波形的时间参数,若干个寄存器对应于一相驱动脉冲。当有限状态机模块中的行计数器和列计数器的状态与某些脉冲参数寄存器的设置相同时,相应的输出脉冲发生翻转。对于不同规格和品牌的液晶显示器这些参数是不同的,即使对于同一产品,在不同扫描模式下它们也是不同的。

3.2 有限状态机模块

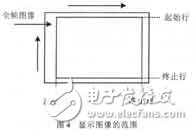

有限状态机由两个16位的行列计数器组成,状态变量为模式寄存器的状态/复位位。在工作模式下,两个计数器循环计数。当行计数器状态与起始行寄存器相同时,行有效信号变高,表示该帧图像的显示开始,此时数据处理器模块开始工作。在系统复位或行计数器状态与终止行寄存器相同时,行计数器被复位。在行有效信号变高后,当列计数器状态与起始列寄存器相同时,像素有效信号变高,表示该行的有效显示开始,此时数据处理器开始输出每个像素的颜色数据。在系统复位或列计数器状态与终止列寄存器相同时,列计数器被复位。

3.3 数据处理器模块

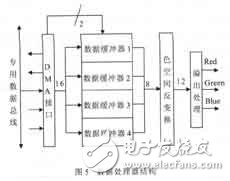

数据处理器模块如图5所示。它由三部分组成:DMA接口及其数据缓冲器、色空间反变换电路和溢出处理电路。根据系统设计要求,由电荷耦合器件(CCD)图像传感器采样得到的原始图像经过像素处理器模块的内插和色空间变换后,成为了YCbCr格式的图像,根据JPEG标准,从RGB到 YCbCr的色空间变换遵循公式[3](1)。

Y=0299R+0587G+0.114B

Cb=_0.169R-0.331G+0.5B (1)

Cr=0.5R-0.4186F-0.0814B

同时为了存储方便,将变换得到的Y信号减去了128,这样三种信号的值均在-128到+127之间,从而都可以用8位的带符号数表示。在存储YCbCr 信号时像素处理器模块将相邻像素的色度信号取均值然后进行复用,这样节省了存储空间。所以在图像存储器中相邻两个像素的亮度信号组合成一个16位的数据存放在一个存储单元里,而复用的色度信

号则存放在下一个地址的单元里[3] 。当要用液晶显示器进行图像显示时,先通过连续两次DMA的读操作获得两个像素的亮度信号和色度信号,分别放入16位的数据缓冲器1和2,然后在读取新的两个相邻像素的YCbCr信号并把它们放入数据缓冲器3和4的同时开始处理缓冲器1和2中的数据,于是通过两对数据缓冲器的作用实现了一个简单的流水线操作。在色空间反变换中要实现将YCbCr信号转换成液晶显示所需要的RGB信号,根据公式(1)并进行简化我们可以得到相应的反变换的公式(2)。

(2)

(2)

根据反变换系数的范围,我们将所有的系数值乘上64,然后将乘积的整数部分用一个8位的带符号数表示。在色空间反变换中我们设计了一个9× 8的Booth乘法器,用来实现色度信号和变换系数的带符号乘法运算。为了保证反变换的正确,在运算过程中要进行符号扩展,所以变换所得的RGB信号是12位的带符号数,而最终输出到数模转换器的数据是8位无符号数,因此还要进行溢出处理,将所有的计算结果都限定在0~255范围内。同时由于液晶显示器的公共电极的电位是交流电位,即相邻两行的公共电极的电位是反相的,所以相邻两行的图像数据应该分别以原码和反码输出。

3.4 脉冲发生器模块

脉冲发生器根据有限状态机中行列计数器的状态和波形参数寄存器内的参数,产生各驱动波形,这些驱动波形用于驱动液晶显示模块本身及其外接的模拟前端电路。

4 Verilog语言实现和FPGA硬件验证

在确定了整体以及各功能模块的结构设计之后,就可以用Verilog HDL语言对设计进行RTL建模,然后用Synopsys 公司的VCS对设计进行仿真并调试。通过RTL级的仿真后,我们对此电路进行了FPGA的硬件验证,使用的芯片是Xilinx公司的VirtexE1000-BG560,系统时钟为54MHz。无论是单独测试还是作为整个数码相机专用芯片的一部分,液晶显示控制电路都能成功实现两种工作模式下的设计要求,性能良好。

5结束语

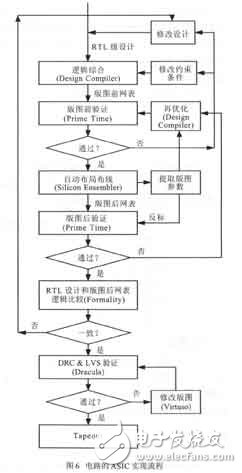

通过FPGA验证后,液晶显示控制电路用TSMC 0.25mm SAGETM工艺实现,后端流程如图6所示,其中的Design Compiler,Prime Time和Formality是Synopsys公司的产品;Silicon Ensembler和Virtuso是Cadence公司的产品。图像采样接口的电路规模为15000门左右,芯片面积为0.49mm×0.8mm。

- 基于CSU8RP3429的LCD移动电源设计(06-10)

- LCD液晶显示器在电机软起动器中的应用(06-14)

- LCD液晶拼接与DLP背投及PDP等离子技术对比(06-13)

- 四大主流大屏显示技术对比分析(06-15)

- 平板电脑LCD显示屏技术解析(06-15)

- DLP投影机和LCD投影机的区别和特点(06-15)