基于CPLD技术的MOSFET器件保护电路的设计方案

扰信号;SIG1_OUT-输出信号1;SIG2_OUT-输出信号2;ENVEOUT-控制信号;TEST1-10ms包络信号、输出信号包络和高电平检测信号的与;TEST2-高电平检测信号;TEST3-信号包络检测信号。SIG1_OUT、SIG2_OUT和ENVEOUT信号进入MOSFET功率管驱动芯片输入端,其输出是MOSFET的输入信号。

图7中三角形符号输出表示的是对输入信号增强驱动能力;矩形表示的是逻辑模块;其他图形标识的是输入输出和逻辑符号。逻辑图的五大功能模块介绍如下:

①分频模块:

该模块的功能是起到分频作用,保证每个模块在做延时的时候误差保持在要求的范围内,还能够保证占用系统资源很小。

②10ms包络模块:

该模块的功能是使输出信号的脉冲宽度不会大于10ms,根据时钟频率产生一个10ms的包络信号与信号包络模块的输出信号相与,就会得到一个10ms的包络,在没有信号输入的情况下,输出为低。

③根据信号产生包络模块:

该模块的功能是根据输入信号,输出一个与输入信号同相位的包络信号。没有信号输入的情况下,输出为低。

④连续高电平检测模块:

该模块的功能是检测输入信号是否是连续高电平,如果是连续高电平,使输出为一个脉宽很窄的信号,然后拉低,在没有信号输入的情况下,输出为低。

⑤200ms死区模块:

该模块的功能是产生一个200ms的死区,即输出有200ms的时间为低电平,该模块是根据信号的下降沿来出发的,当输入信号下降沿到来的时候,输出拉低,并保持200ms时间,200ms过后,输出置高。

4.试验验证

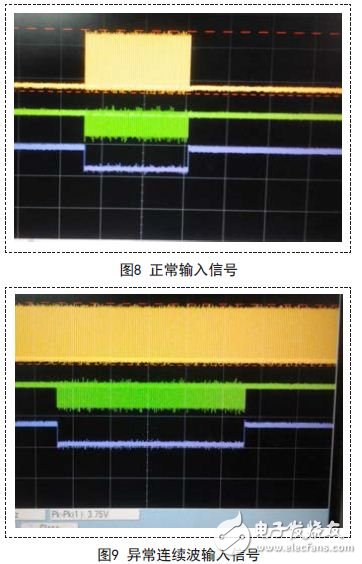

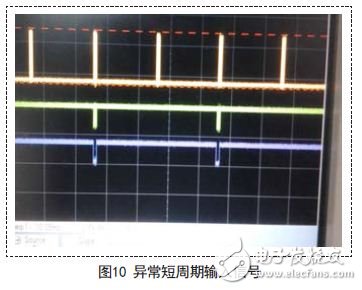

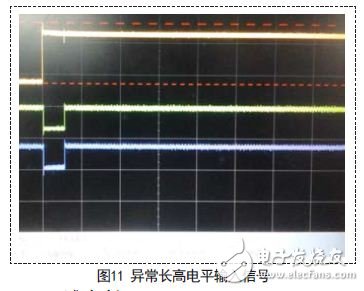

在功率MOSFET保护电路输入端分别输入正常信号、连续高电平、连续波信号和短周期的脉冲信号。在没有保护电路的情况下,若输入端输入这几种异常信号,发射机功率MOSFET电路必将烧毁。保护电路输出经光隔隔离并高低电平转换后驱动MOSFET工作。在试验室情况下,各种情况的正常、异常输入信号经CPLD保护电路后输出信号实测波形如图8~11所示。

第一路是原始输入激励信号,第二路是保护电路的输出信号,第三路是包络信号。

由图中可知,异常信号经CPLD保护电路逻辑处理后,输出满足系统要求并且使功率MOSFET可以接受的输入信号。

5.结论

本文提出了采用CPLD芯片解决大功率发射机激励信号异常或故障带来重大危害的方法。通过系统模拟测试以及实际拷机测试,验证了本设计的正确性和可行性。现已将此设计应用于某大功率发射机项目的保护电路中,最大限度减小了因激励信号异常和故障给发射机带来的危害。另外,本设计的硬件电路具有较强的通用性,只需稍加改变软件编程,就可以应用于其他电路的信号处理设计中。

- 运放电源过压保护电路设计(06-28)

- 数控用开关电源保护电路的实现(11-23)

- 开关电源的过流保护电路设计(12-21)

- 锂电池过充电、过放电、短路保护电路设计(02-20)

- 开关电源保护电路实用设计方案(09-23)

- 电瓶电压缺电的保护电路设计(09-02)