射频识别芯片设计中时钟树功耗的优化与实现

port_clock_gating

这个阶段的目的是通过综合工具(DC)进行门控单元的自动插入,以便进一步减小功耗。

需要注意的是对插入ICG的参数的设定,比如maximum fanout(扇出越大越节省功耗,扇出越平衡skew越小,视设计而定,如图所示),以及minimum_bitwidth参数的设定,另外对于较复杂的门控结构需要插入常开ICG以使时钟网络结构更加平衡。

4.3 时钟树综合阶段优化功耗

图5 两种时钟树结构对比(a):多级纵深型;(b):少级扁平型

先介绍一下时钟树综合参数对时钟树结构的影响:

Skew :时钟偏移,总的时钟树综合目标。

Insertion delay(Latency):时钟路径总延时,用于限定时钟树级数的增加。

Max taranstion:由最大转换时间限定一级buffer能驱动的buffer 的数量。

Max Capacitance Max Fanout:由最大负载电容、最大扇出限定一级buffer 能驱动的buffer 数量。

一般设计中的时钟树综合以降低时钟skew为最终目的,加大level级数,减小每级fanout,将投入较多buffer,更精确的平衡每条时钟路径的 latency,从而得到较小skew。但是对于低功耗设计,尤其是当时钟频率较低的时候,时序要求并不是很高,所以希望能减小时钟树的规模以减小时钟树带来的动态翻转功耗。如图所示,通过减小时钟树level级数,加大fanout可以有效减小时钟树的规模,但由于buffer 数量的减少,较之多级结构的时钟树,级数较少结构的时钟树只是大概平衡每条时钟路径的latency,得到的skew较大。可见,以降低时钟树规模为目标,进行低功耗时钟树综合是以增大一定的skew为代价的。

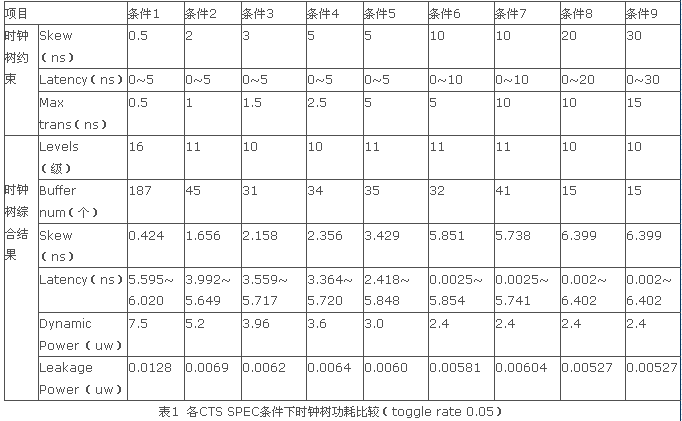

具体到本RFID芯片,我们采用了TSMC 0.18um CMOS LOGIC/MS/RF工艺,时钟频率只有1.92M,是非常低的,此时时钟进行时钟树综合时,采用以降低时钟树规模为目标的低功耗时钟树综合,主要对 skew,latency和transiton这几个约束进行了设定,由于约束fanout会带来时钟树级数的增加,带来功耗的增加,所以没有设定这个值,采用库里的默认值。在实际中,我们使用了9种不同的时钟树约束条件,约束条件及综合结果如表1 所示。

5 结论

如表1所示,总的趋势就是target skew设的越大,最终的时钟树规模越小,时钟树buffer数量越小,对应的动态静态功耗也越小,这样就达到了节省时钟树功耗的目的。可以看到当target skew大于10ns后,功耗基本不再变化,但是基于大的skew值会带来hold时序的变差导致修复时序的时候插入buffer增多,所以应该进行折中,从图表来看策略5和策略6为优选方案。另外当skew设置选出最优后,还可以看到Max transition值设的越大最终得到的功耗也越小,这可以理解为时钟信号跃迁的时间越长所需要的能量越小。另外latency约束的设置可以尽量放大,其值的大小对最终的功耗结果影响不大。

作者 常晓夏,潘亮,李勇

射频识别芯片 UHF RFID 动态功耗 芯片设计 相关文章:

- RFID技术在电力资产管理系统中的应用(04-01)

- Gerry Weber商店采用ENSO detego的RFID软件(02-23)

- RFID技术让现实版马里奥赛车成为可能(03-02)

- 无线射频识别技术在低碳智能交通中的应用(02-02)

- 采用电子标签技术辨识新式军车牌号的真伪(03-28)

- 智能泊车管理导航系统的设计案例(04-18)