基于SPI FLASH的FPGA多重配置

现代硬件设计规模逐渐增大,单个程序功能越来越复杂,当把多个功能复杂的程序集成到一个FPGA上实现时,由于各个程序的数据通路及所占用的资源可能冲突,使得FPGA控制模块的结构臃肿,影响了整个系统工作效率。

通过FPGA的多重配置可以有效地精简控制结构的设计,同时可以用逻辑资源较少的FPGA器件实现需要很大资源才能实现的程序。以Virtex5系列开发板和配置存储器SPI FLASH为基础,从硬件电路和软件设计两个方面对多重配置进行分析,给出了多重配置实现的具体步骤,对实现复杂硬件设计工程有一定的参考价值。

0引言

现代硬件程序设计规模越来越大,功能越来越复杂,当多个应用程序同时在一个硬件平台上实现时,各个程序的资源使用和数据通路可能会冲突,这增加了控制电路设计的复杂程度,给开发人员增加了工作量和开发难度。通过多重配置,可以将多个应用程序根据需要分时加载到FPGA中,不仅精简了电路设计,而且使系统更加灵活。FPGA多重配置的特点可以让特定条件下的用户选择片上资源不多的FPGA去实现需要很多资源FPGA才能实现的功能,这大大降低了开发费用,同时提高了FPGA的利用率。

Xilinx公司Virtex5系列的FPGA具有多重配置的特性,允许用户在不掉电重启的情况下,根据不同时刻的需求,可以从FLASH中贮存的多个比特文件选择加载其中的一个,实现系统功能的变换。

1总体设计

当FPGA完成上电自动加载初始化的比特流后,可以通过触发FPGA内部的多重启动事件使得FPGA从外部配置存储器(SPI FLASH)指定的地址自动下载一个新的比特流来重新配置。FPGA的多重配置可以通过多种方式来实现。本文采用的是基于ICAP核的状态机编码方式。通过调用Xilinx自带的ICAP核,编写状态机按照一定的指令流程对ICAP核进行不断的配置,可以控制FPGA重新配置。这种方式可以在源代码中加很多注释,让后来的开发者很清楚地明白ICAP核指令流顺序,以及多重配置地址计算方法,是一种简单实用的实现方法。

1.1硬件电路

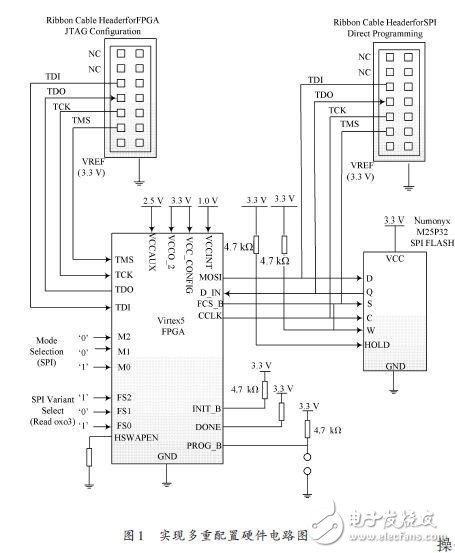

多重配置的硬件主要包括FPGA板卡和贮存配置文件的FLASH芯片。FPGA选用XILINX公司Virtex-5系列中的ML507,该产品针对FPGA多重配置增加了专用的内部加载逻辑。FLASH芯片选用XILINX公司的SPI FLASH芯片M25P32,该芯片存贮空间为32 Mb,存贮文件的数量与文件大小以及所使用的FPGA芯片有关。实现多重配置首先要将FPGA和外部配置存储器连接为从SPI FLASH加载配置文件的模式。配置电路硬件连接框图如图1所示。

在FPGA配置模式中,M2,M1,M0为0,0,1,这种配置模式对应边界扫描加上拉,FPGA在这种模式下所有的I/O只在配置期间有效。在配置完成后,不用的I/O将被浮空[5].M2,M1,M0三个选择开关对应于ML507开发板上的SW3开关中的4,5,6位,在FPGA上电之前将上述开关拨为0,0,1状态。

1.2软件设计

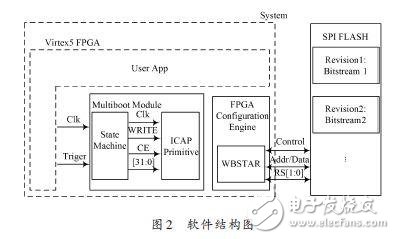

从软件设计的角度可以将FPGA多重配置主要分为两个部分。第一部分是用户自己开发的程序,这一部分包括用户要在FPGA上边实现的功能,同时也包括为重载模块提供时钟信号,以及触发信号,本文触发信号是通过用户程序编写串口通信协议栈来接收PC端传输的数字作为触发信号。第二部分是FPGA重载配置模块。FPGA多重配置首先要调用ICAP核,当满足触发条件后,采用状态机编码的方式对ICAP核进行赋值配置。FPGA多重配置的软件结构图如图2所示。

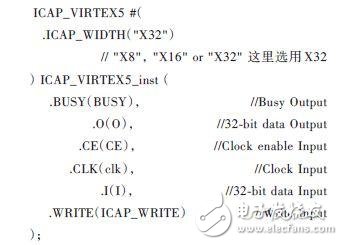

重载模块首先要调用ICAP核。ICAP原语在Xilinx的编译软件ISE中调用,调用路径为Edit→LanguageTemplates,VHDL/Verilog→Device PrimiTIve InstanTIa-TIon→Virtex5FPGA→Config/BSCAN Components→In-ternal Config Access Por(t ICAP_VIRTEX5)。

ICAP_VIRTEX5调用接口如下:

ICAP核支持X8,X16,X32三种数据带宽模式。在整个FPGA重配置的过程中并没有用到ICAP核的输出,因此在重载模块的状态机控制程序中不关注BUSY,O信号的值,可以不对它们赋值。用户程序在使用接口时只需对CE,CLK,I,WRITE4个信号不断赋值来发送命令。

在调用了ICAP核接口之后,通过Verilog编码的方式实现状态机。通过状态机发送IPROG指令给ICAP核,ICAP核在接收到这些指令后会根据指定的地址自动加载配置文件。

IPROG指令的作用是对FPGA芯片进行复位操作,该复位操作对FPGA内部的应用程序进行复位,复位过程中除专用配置管脚和JTAG管脚,其他输入/输出管脚均为高阻态。完成复位操作后,将默认的加载地址用热启动地址寄存器(Warm Boot Start Address,WB-STAR)中的新地址替换。

在发送IPRO

- Xilinx Kintex UltraScale 一半尺寸的 PCI Express 平台 (HTG-K816)(06-15)

- Xilinx全新参考设计提供业界首个单芯片400G解决方案(02-12)

- Xilinx用于工业自动化的机器视觉解决方案(11-30)

- Xilinx多协议机器视觉摄像机参考设计(12-01)

- 机器视觉技术原理解析及解决方案集锦(02-06)

- 机器视觉在汽车电子方向的应用解决方案(02-13)