基于ADPCM的数字语音存储与回放系统设计方案

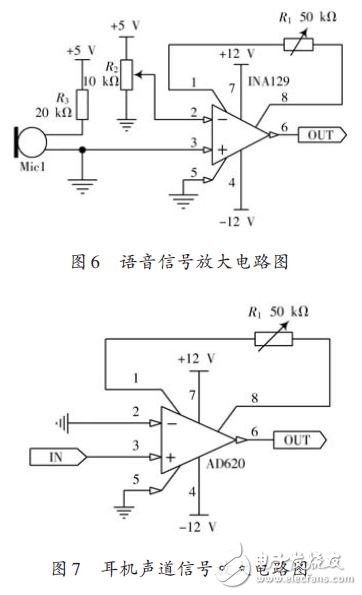

本的AD620、INA129.对于调制电阻RG ,通过增益计算公式G = 49.4 kΩ/RG + 1 可以计算得到, RG 使用50 kΩ可调电位器来达到2.5 倍的增益放大,电路设计图如图6,图7所示。

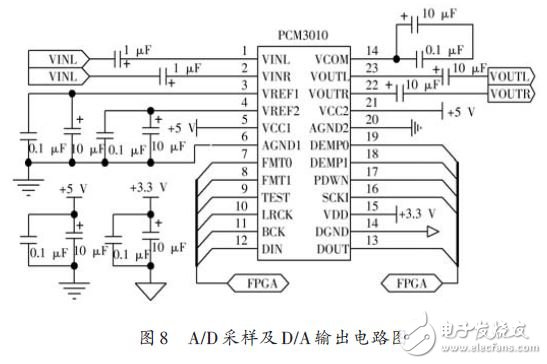

3.2 A/D及D/A设计电路

PCM3010 为24 b 立体声音频编码器,其内部包含Σ-Δ 型ADC和DAC.其中立体声ADC输入信号峰峰值为3 V,内置抗混叠滤波器和高通滤波器,采样速率为16~96 kHz可调,立体声DAC输出信号峰峰值为3 V,内置去加重滤波器,转换速率为16~192 kHz可调。DAC输出信号接后置低通滤波器,可实现较好的波形输出。

该芯片将ADC、DAC集成一体,极大地简化了硬件电路规模,并且价格便宜,具有极高的性价比。这里在某些数据线与控制线上串接了一个小电阻,以降低信号上下边沿的跳变速率。其电路图如图8所示。

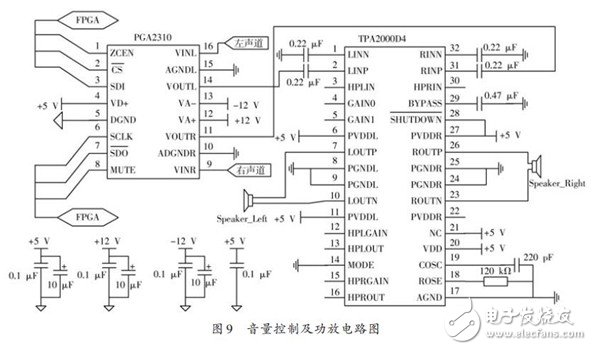

3.3 音量控制及功放电路

音量调节选用高性能立体声音频音量控制芯片PGA2310实现。通过数字方法控制模拟音量,每声道音量单独可调,并具有静噪功能。它具有极宽的增益衰减范围,-95.5~31.5 dB 以0.5 dB 步进可调,失真度仅为0.000 4%.其输出两路信号送入高效D 类音频功率放大器TPA2000D4,+5 V 供电驱动4 Ω负载时功率可达2 W.其静态功耗低,外接电路简单,无需外接LC输出滤波器,即可直接驱动扬声器。电路图如图9所示。

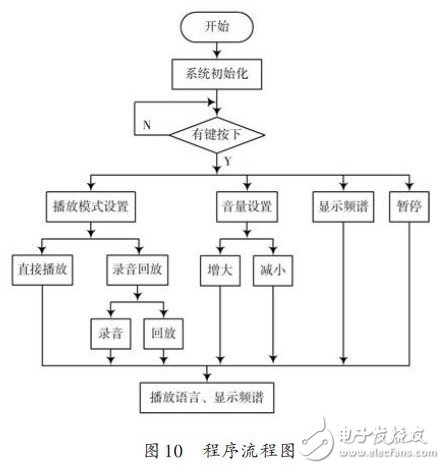

4 程序设计

系统软件部分由单片机的 C51语言和FPGA的Ver-ilogHDL语言组成。其中,单片机主要完成用户输入输出处理和系统的控制,FPGA主要完成需要严格时序控制(如数据采集、频谱显示)以及大规模数据计算(如FFT、ADPCM 编码)等。整个系统的设计中模块化思想贯穿始终,采用菜单键选择所用功能,系统流程图如图10 所示。

5 方案测试与结果

5.1 测试仪器

测试仪器包括直流稳压稳流电源,型号为SG1733SB3A;60M 数字存储示波器,型号为TektronixTDS1002;秒表。

5.2 方案测试与结果

5.2.1 语音存储与回放效果测试

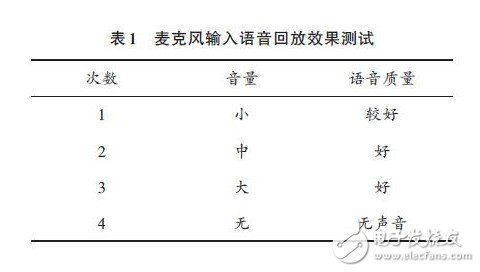

(1)一名组员面对麦克风以不同大小的声音说话,录下一段语音,记录回放语音的效果,结果见表1.

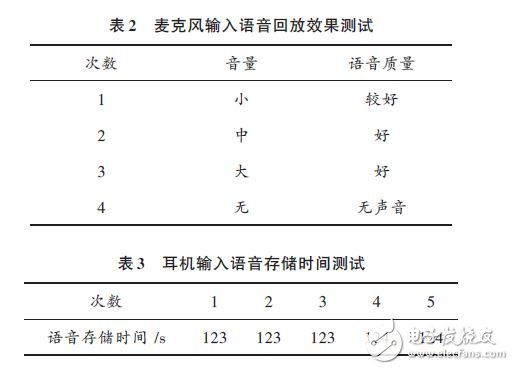

(2)由耳机输入不同音量的立体声音乐,录下一段语音,记录回放语音的效果,结果见表2.

5.2.2 语音存储时间测试

(1)由耳机不间断地输入立体声音乐,启用录音模式,待系统显示存储器存满后,回放语音,用秒表记录语音回放最长时间,结果见表3.

(2)一名组员面对麦克风不间断地说话,启用录音模式,待系统显示存储器存满后,回放语音,用秒表记录语音回放最长时间,结果见表4.

5.2.3 语音频谱分析及显示测试

由耳机或麦克风输入一段语音信号,由扬声器直接播放出来,同时在示波器上实时显示频谱。测试结果为当播放的声音变化时,可观察到频谱有相应的明显变化。

由于不能明确知道语音信号的实时频率和幅度信息,故只对频谱进行了定性测试。

6总结

该系统设计方案实现了语音存储及回放,最长存储时间达2 min,回放语音效果清晰良好,并能在示波器上实时显示语音频谱。采用ADPCM 编码在保证回放音质的情况下,极大地提高了存储器的利用率,并通过对语音信号采用分帧加窗的方法实现了短时频谱分析。

另外,系统采取了一系列抗干扰措施以减小噪声,如数字地与模拟地分开走线,在一点汇合;电源处采用一个10 μF和0.1 μF的电容并联去耦;时钟走线尽量短等。但系统在语音回放时仍存在一定的噪声,尤其当输入语音音量较小时,噪声更为明显,这是本方案需要完善的地方。

- 基于MSP430的语音与音频压缩/解压缩技术(08-12)

- 单片机在电源设计中的应用(06-07)

- 基于单片机的锅炉液位控制装置设计(07-22)

- 基于SPWM的交流稳压电源设计方案(09-15)

- 基于单片机的电池保护电路系统设计(02-24)

- 晶闸管三相全控桥式整流电路的直流电源设计(02-08)