新封装理念:采用紧凑式SIP的QFN封装

以下说明"采用紧凑式 SIP 的 QFN 封装"封装设计与市场中现有的 SIP 封装的细小差异。

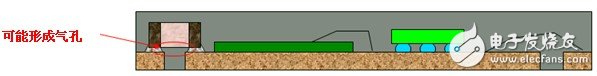

图 8 "采用紧凑式 SIP 的 QFN 封装"封装设计与市场中现有的 SIP 封装的细小差异

采用紧凑式 SIP 的 QFN 封装:

+ 突破灵活性和封装/产品可扩展性的限制 à 可使用更大、更厚的无源元件尺寸,利于扩展产品和改善性能。

+ 产品性能和应用 à 无源元件能够尽可能地靠近有源芯片进行安装,从而获得最佳的产品性能。例如,DrMOS 要求元件尽可能地靠近 HS 芯片的漏极和 LS 芯片的源极。

+ 上市时间 à 可快速制造出产品扩展或使用更厚元件的样品

+ 可靠性 à 未采用复合物成型封装,避免无源元件与引脚框之间形成封装气孔类似于印刷电路板上的无源元件

图 9 采用紧凑式 SIP 的 QFN 封装

市场中现有的 SIP:

- 封装/产品的灵活性和可扩展性差 à 受限于封装厚度,无法使用较大、较厚的无源元件,不适于产品扩展。

- 导电路径较长,电阻较大。信号传输质量/效率必然因此受到影响。

- 由于需要构建新封装平台和引进成型模具,上市时间较长。

- 可靠性 à 由于无源元件与引脚框表面间的间隙会导致形成封装气孔,在压力测试过程中可能存在"爆米花"效应风险。

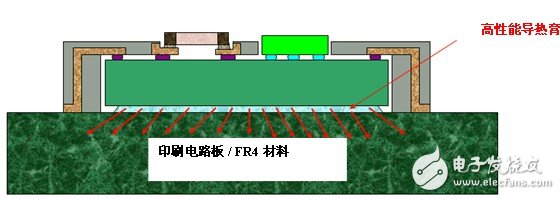

对于高发热量芯片应用,可在有源芯片的背面涂覆额外的高性能导热膏,从而增强热性能(图 10)。

图 10 对于高发热量芯片应用,可在有源芯片的背面涂覆额外的高性能导热膏,从而增强热性能

工艺流程:

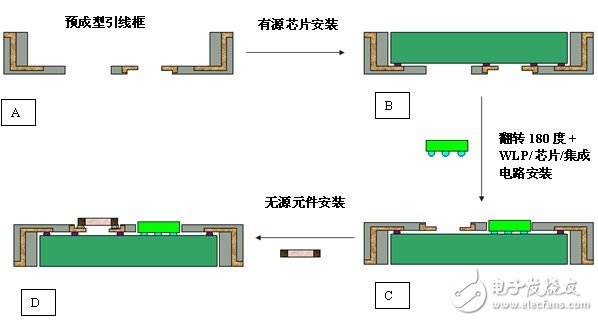

"采用紧凑式 SIP 的 QFN 封装"可简化装配工艺。下图展示装配工艺流程的诸多概念之一(图 11)。

图 11装配工艺流程的诸多概念之一图示

工艺流程描述:

A – B 有源芯片通过锡球焊接、丝网印刷、印刷电路板装配 (PCBA) 或其他市场中现有的布线工艺安装于预成型引脚框中。

B – C ‘A – B’ 中所述的预成型引脚框随后进行 180 度翻转以便将其他芯片、WLP、IC 产品或其他元件安装到有源芯片表面上的 I/O 叉状物。

D: 无源元件或其他半导体封装随后将通过锡球焊接、丝网印刷、印刷电路板装配 (PCBA) 或其他市场中现有的布线工艺安装于预成型引脚框中。封装(框式)将被送至下一流程,例如封装切割、测试、印制标记和包装。

- 一文看懂有源元件和无源元件的区别(06-11)

- 学好嵌入式系统电路入门之——无源元件(06-19)

- 基于OSP在印刷电路板的应用(05-16)

- 不同的GND在印刷电路板,都会不同(08-21)

- 印刷电路板基材选择及主要类别(09-09)

- 屏蔽技术应用于高频变压器中的设计方案(12-23)