可编程时钟振荡器用作FPGA系统的时序参考有何优势?

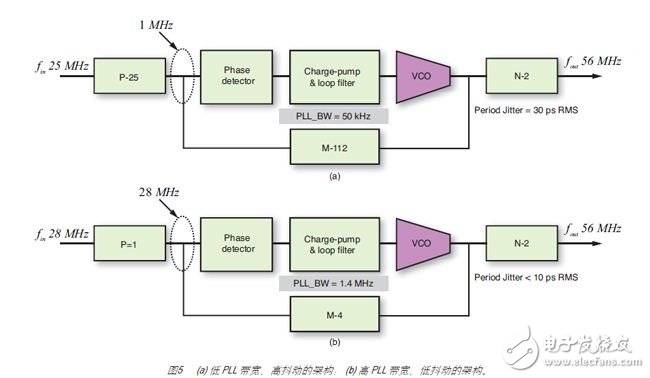

第二种方法可以最小化 P 值而且能实现更高的 PLL 带宽,从而可以降低输出周期抖动。

大多数可编程振荡器采用一个谐振器单元和一个或多个 PLL 来对不同频率进行综合。传统上,石英晶体通常被选定作为稳定谐振器。不过,其封装难题却限制了此类可编程振荡器的可用性。近期,硅 MEMS 振荡器大量上市,能够在稳定谐振器与高性能 PLL 方面提供高性价比的完美组合,并且适用于众多行业的标准小型封装。这种振荡器为优化 FPGA 系统中的时钟树提供了出色的FPGA 时钟解决方案。此类时钟还可以满足高速收发器更加苛刻的抖动规格要求。

EMI消减

只要在可编程振荡器中将稳定谐振器与高性能合成器配合使用,就能够轻松获得许多其它有用的时钟功能。其中之一就是用于消减EMI的扩频时钟(SSC)。

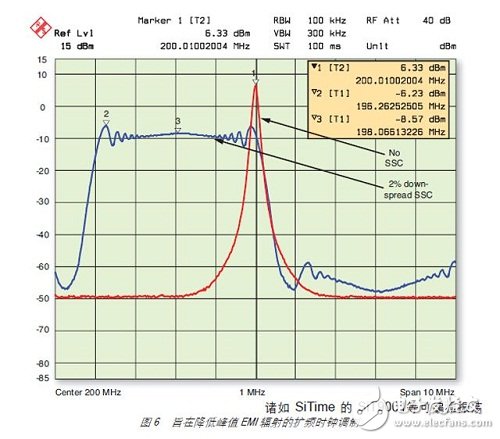

SSC 振荡器是一种频率经过调制的时钟,可以确保时钟信号能够在更大的频率范围内传播,从而可以减少给定频率范围内的整体峰值电磁辐射。SSC的作用在基于 FPGA 的系统中更加明显,因为它可以减少共享同一时钟源的所有电路与 I/O 的 EMI。相比而言,跟踪滤波与升高/降低控制法只能降低系统特定部分的 EMI。图 6 说明了 SSC 如何降低峰值 EMI 辐射。

SSC 中的重要参数是调制范围与调制方法(中心扩频或向下扩频)。诸如 SiTIme 的 SiT9001等可编程振荡器可提供宽广的 SSC 调制范围——向下扩频和中心扩频方式下都可以达到0.5%~2%。这种菜单选择方式使设计人员能够在优化 SSC 实现最佳系统性能的同时将 EMI 最小化。

可编程振荡器中分数 N PLL 所带来的有用功能的另一个例子是数控振荡器(DCO)。DCO 功能强大,结合 FPGA,可实现低带宽、全数字 PLL,从而能够为高端电信与网络系统提供失效保护、故障切换或抖动消除等功能。

硅 MEMS 的优势

全新的硅 MEMS 振荡器在过去几年里显著扩大了商用可编程振荡器的产品组合。这些振荡器使用户能够定制参考频率, 选择外部参考与FPGA 内部 PLL 参数的最佳组合,从而实现最佳的时钟树设计。此外,设计人员还可以轻松选择电源电压、封装、温度范围、频率稳定度和驱动强度以满足应用需求。这些振荡器的可编程特性还能够缩短研发周期,实现快速原型设计以及加快生产进度。

SiTIme 的单端和差分硅 MEMS 振荡器已经应用到赛灵思的部分演示板中。目前已经可以针对不同频率、电压和封装需求订购此类部件,以实现最佳的系统性能。

作者:SiTIme 公司战略应用总监Sassan Tabatabaei

- 时钟振荡器的原理与作用详解(08-24)

- CPCI总线的分布式系统设计应用(06-02)

- 工控机在IC卡加油工程中的应用(05-13)

- 基于PCI-9846武器数据链测试技术的研究及实现(11-26)

- PCI总线接口技术及其在高速数据采集系统中的应用(11-08)

- 基于PCIe的WarpDrive SLP-300加速卡(10-23)