TI专家分享:如何进行单片FPGA电源解决方案的实施?

2633三开关式/线性控制器电源

对于一些仅需要一个次1.25V输出的双同步降压控制器的应用而言,LM2657提供了一种引脚数目封装更少的优秀替代方案。对于那些需要三个或者四个轨的更低功耗应用,LP3906也是一种优异的替代方案,它拥有两个全集成1.5A同步开关式输出和2个300mA LDO输出,所有这些都包括在一个单封装中。

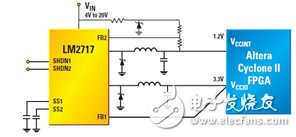

如前例所示,目前大多数FPGA均要求1.50V、1.20V甚至更低的内核电压(如Xilinx最新的Virtex 5系列FPGA,其拥有一个1.0V 65nm内核)。市场上的许多稳压器均有一个1.25V的常规带隙基准电压。图4和5显示了如何利用常规带隙IC(如LM2717)驱动这类次带隙数字负载的简化结构图例子。电压转换器的基本工作原理仍然相同,但是参考电阻式分压器对稳压器输出电压进行编程的方式不同。

LP3879特性

l LP3879 800mA LDO拥有±1%初始输出精度

l 输入电压:2.5V到6.0V

l 自定义电压从1.0V到1.2V

l 关机静态电流小于10µA

l 18 µV低输出降低噪声

l 可用于PSOP-8和LLP-8面贴封装

在任何闭环稳压器电路中,将输出电压经过电阻分压器降压调节以后,再同某个内部基准电压进行比较。如果该基准电压为1.25V,则需要对输出电压的降压后采样(通过FB引脚注入至稳压器IC)进行设置,以匹配该值,从而维持调控。在典型系统中,该FB分压器放置在输出(最高电势)和接地(最低电势)之间,因为FB电压(1.25V)维持在该范围内。在要求输出电压低于内部基准值的系统中,我们仍然需要向FB引脚提供一个匹配电压(1.25V),但是该值不会降至VOUT(现在更低)和接地之间。通过在VOUT(现在变为最低电势和分压器的低端)和任何1.25V以上辅助电压(起高电势作用)之间放置分压器,可以实现上述目标。

图5所示举例使用阿尔特拉公司的Cyclone II 1.20V FPGA和国家半导体公司的LM2717,旨在说明这种配置的最简单实现方法,其高压为3.3V轨本身。这种轨的充分滤波和良好布局很重要(我们建议,去耦陶瓷电容器靠近电阻式分压器低端接触3.3V轨的地方),因为次带隙输出的调节依赖于该轨的稳定性。排序也很重要,因为3.3V轨需要在内核电压输出开启以前出现以实现正确的调节。

图5 使用3.3V轨作为次1.25V内核电压生成辅助电压的LM2717 1.2V内核、3.3V I/O双集成开关式FPGA电源

在大多数FPGA中,额定1.20V或者1.0V内核电源电压需要稳定在±50 mV或者±60 mV以内,因此所有瞬态、纹波和容差变化需保持在该限制内。

图6 一个LM4040分流基准用于次1.25V内核电压生成的LM2717 1.2V内核、3.3V I/O双集成开关式FPGA电源

图6显示了一种使用独立电源为辅助轨供电实现次带隙输出的替代方法,此处为一个小型、低成本分流基准(精密齐纳二极管),例如:LM4040CIM3-2.5 (0.5%)或者LM4040DIM3-2.5(1%)。这种方法让3.3V输出中出现的潜在瞬态不会交叉耦合至1.20V输出调节。另外,它还允许3.3V轨在1.2V轨之后上电,或者在不妨碍1.2V输出调节的情况下在任何时间关闭。这种输出的精确度依赖于选定电压基准的线压调节。由于在应用中内核电压精度很重要,因此选择正确的电压基准是关键。

现在,设计人员可以利用多种资源设计出适用于他们的应用的最佳电源。例如,TI公司的"电源专家"(Power Expert)软件工具通过选择FPGA、电源和工作条件,最后给出符合设计人员重要要求的电源IC解决方案建议,说明其是否可以达到最大效率以及设计是否简易。另外,它还连接到TI的WEBENCH设计环境,围绕选定稳压器IC和电路模拟选择组件。

- 为EMI敏感和高速SERDES系统供电(08-17)

- 虚拟远端采样控制器惠及视频安保(10-26)

- 固定频率工作的降压稳压器设计(11-23)

- 稳压器的输出电压精度是否糟糕(11-03)

- 汽车稳压器适应极端环境的设计方案(12-30)

- 高功率密度、双通道 8A μModule 稳压器(01-10)