2032年的FPGA:ACM FPGA 2012年度研讨

括本地存储器、互联和规模很大的同构FPGA。

Blainey解释说,这类FPGA将成为服务器的虚拟资源:一种受保护的虚拟架构,在这种架构上,系统软件可以动态建立可共享的加速器。这类器件实际上汇集了大量可动态重新配置的逻辑门,由基于硬件的系统管理程序进行管理,对逻辑门的建立、拆除、共享和安全进行控制。

这两类完全不同的体系结构之间也有其微妙之处。总体上,考虑SoC替代的设计人员,例如,移动设备和嵌入式计算领域的设计人员,倾向于认为未来的FPGA是关键位置具有逻辑架构的ASSP。认为在FPGA架构中直接实现软件的设计人员倾向于未来是同构架构,具有很大的I/O带宽。正如FPGA大会将要发表的论文所述,还有一些团队尝试怎样实现硬核IP资源,例如,在可综合处理阵列中实现存储器模块和DSP流水线,在软件用户中实现异构价值。

设计隐喻和工具

虽然在体系结构上有各种不同的观点,但是在设计人员用于表达系统所使用的工具以及隐喻上却有比较一致的看法。这种一致性的起点是,寄存器传送级(RTL)作为表达系统的一种方法,已经不够用了。Tabula总裁兼CTO Steve Teig认为:"当需要对FPGA编程时,RTL用起来很差。而C语言更差。虽然从串行转向并行执行是非常底层的工作。Haskell等功能语言要好一些,但是,我认为λ-calculus仍然不是最好的抽象表达方式,这是一种大部分功能语言都以其为基础的算术抽象语言。"

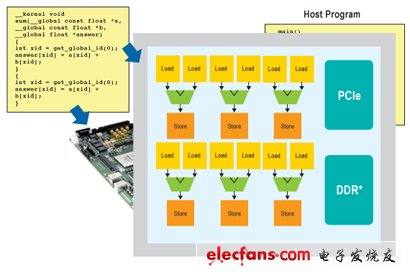

Blainey也同意这种看法。他预测,以后将广泛的采用显式并发语言,通过库和编译器将软件转换为FPGA结构。此外,会有很多功能语言编程精英来解决这类问题。Altera的Burich和Xilinx的Bolsens都认为,今后更多的设计会定位于显式并行命令式语言,例如,OpenCL (图2)等,他们都宣称他们的公司正在从事这方面的工作。

图2. 将OpenCL代码编译到FPGA的并行结构中

其他演讲人描述了完全不同的FPGA设计概念。Shep Siegel是Atomic Rules公司的创始人兼CTO,描述了一种可重用平台,每一种FPGA实现都包括具有可动态重新定位功能的库。Siegel认为:"还是需要RTL,但是,同步设计的概念只是一种隐喻。我们将扩展全局异步本地同步的(GALS)概念。而我们所关注的是弹性流水线和延时不敏感设计,我们使用时间戳来维持系统同步。"

Maxeler技术公司主席Michael Flynn和斯坦福教授Emeritus表达了相似的观点。采用高性能计算加速器,Flynn的团队将算法简化为数据流图形。Flynn解释说:"他们采用Java描述图形中的节点,建立非常长的流水线,复制到矢量处理阵列中,直到填满硅片。"

Flynn说:"在20年内,所有技术都将是基于阵列的,只是受到软件的限制。一个最大的难题是必须改变编程模型。软件开发在过去20年的发展一直没有处理好并行问题。"

Bolsens还介绍了系统软件面临的另一难题——在20年内将成为高级程序员的这一代会喜欢什么。我们已经过时了。如果您注意一下一个16年的老程序员,您会发现他们安心于异构的环境——Java、Perl、Python,等等。他们会选择一种库、应用程序或者他们能找到的一类代码。

缺少的环节

几名演讲人还介绍了目前的技术以及2032未来技术之间一些未能解决的关键问题——从系统非常抽象的视图到器件编程文件等。

Bolsens说:"必须通过研究填补软件和硬件设计之间的空白。"Blainey还介绍了可综合加速器的问题,他认为这是未来服务器堆叠中动态重新编程难以解决的问题。Flynn列举数字说明了这一观点:"今天,我们的布局布线需要运行数十个小时。那么,到2032年,是不是要运行一个月?供应商应该把这些工具置入到云中。"

Cheung的概念是通过常数可重新配置功能保持硅片工作,而且还假定了某类动态重新编译功能,进一步发展了这种观点。他认为:"我们将看到所有这些东西连接起来,这样,有足够的资源来管理重新配置问题。"他的观点是,每一电子系统中都会有机械智能功能,云不再是服务器的远程堆叠,而是扩展到互联设备群中。这种观点在支持泛在计算之前就有了,但是,Cheung认为处理亚2-nm技术必须要采用这种观点。

总结

总之,研讨发言人认为并不会出现对摩尔定律尺度发展革命性的偏离。但是,在怎样处理大量的晶体管上存在争议,怎样解决尺度带来的新问题。我们应该构建越来越专用的异构混合硬件功能模块和可配置模块?还是,研究大量逻辑门,提高本地逻辑门速率,开发大规模块架构,以实现虚拟加速器?或者,需要可重新配置互联专业知识来保持功能固定芯片不变,从而提高产量

Altera Xilinx 3D CMOS FPGA 相关文章:

- 基于DSP和FPGA的机器视觉系统设计与实现(03-07)

- Altera在OFC 2014上推出400G以上OTN解决方案(02-12)

- Altera Cyclone FPGA典型案例:远程信息处理/娱乐系统(02-23)

- Altera典型车用网关控制器系统简析(02-23)

- 基于Altera ASI IP核的ASI发送卡实现(02-25)

- 基于FPGA的洗衣机控制系统的设计与实现(07-27)