基于32位低端嵌入式系统的图像采集模块

时间:04-29

来源:互联网

点击:

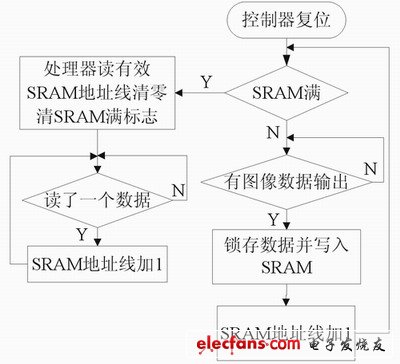

入时钟,来降低CMOS数字图像传感器输出图像的速率。系统中CPLD的时钟采用40MHz,将经过10分频后的时钟作为CMOS图像传感器的时钟。这样降低了图像输出的速率,减轻了处理器进行图像数据处理的负担,使处理器有空闲时间进行其它控制操作。由于CPLD要读取CMOS图像传感器输出的图像数据并缓存到SRAM中,因此CPLD的片内逻辑主要是根据图像传感器输出图像数据的时序和SRAM的读写时序来编写。CPLD片内的控制逻辑电路主要由Verilog语言编写的状态机实现。另外还有一些附加的门电路、多路选择器和加法器,它们和状态机共同组成了系统的摄像头缓存控制逻辑电路。CPLD控制逻辑流程图如图3所示。

图3 CPLD控制逻辑流程图

功能验证

为了验证系统的图像采集功能,需要对CPLD缓存的数据进行处理及显示。由于PC机具有丰富的软硬件资源,因此本文利用PC机来显示图像,验证图像采集功能的正确性。具体方法是:系统主处理器LPC2104读取SRAM中的图像数据并通过串口传送给PC机,在PC机上编写软件接收数据并做简单的处理就可以在PC机屏幕上显示出图像,从而能够验证系统的功能。

结语

本文通过在一个低端的嵌入式处理器系统中添加CMOS数字图像传感器,并编写硬件描述语言程序、嵌入式处理器程序,实现了采集图像的功能。文中给出了一个在低端嵌入式系统中增加图像采集功能的实现方案,该方案具有性价比高,通用性强等优点,可广泛应用于各种基于低端嵌入式处理器的监控系统中,使监控管理人员可以直观地了解被监控的对象。该方案还可以进一步实现许多扩展功能,如图像对比和图像识别等

- 嵌入式系统在电源设计中的运用(09-20)

- 基于4G通信的嵌入式数据通信系统设计(10-10)

- 汽车安全性能亟待升级 嵌入式系统把关护航(05-07)

- USB端口找到新居,落户嵌入式系统(02-11)

- 嵌入式系统在电力变压器监测中的应用研究(09-18)

- 基于OMAP架构的嵌入式指纹识别系统设计与应用(04-29)