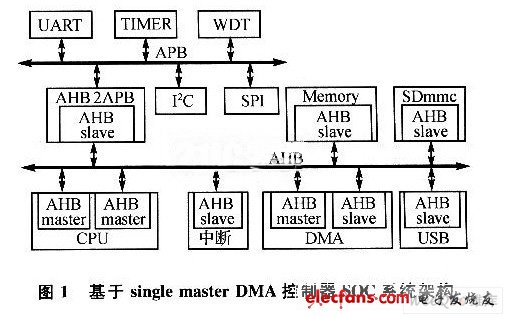

一种提高系统响应速度的SoC系统架构

部配备了容量较大的高速缓存(Cache),当DMA控制器占用内存时,处理器仍可利用Cache中的程序和数据继续运行;但Cache是利用程序的局部性原理,当处理器执行的操作有良好的局部性时,在DMA占用AHB总线期间可以利用Cache里的指令和数据继续运行,但若此时有设备产生中断,此时处理器的PC指针就会产生跳转,从而会产生Cache不能命中的情况。而AHB总线又被DMA控制器占据,处理器不能对外取指,而且Cache的容量因成本问题不可能太大,从而影响处理器的效率。

2.3 包含2个AHB从接口DMA控制器的新型SoC系统架构

为了解决因图1所示架构大批量数据传输而引入DMA产生的问题,提出了包含2个AHB接口的DMA控制器的SoC系统架构。在AHB总线上的sla-ve接口都是不能发起传输的,它的一切操作都是被动的。因此图2中的DMA控制器的主要功能是提供需要进行DMA传输的外设接口与处理器读写主存的通道以及它们间优先级设定。在此双AHB从接口的DMA控制器中处理器优先级永远最高,其他外设通道都可以相互设置优先级,而且除处理器外,为了防止同一个外设长期占用DMA总线的使用权,可对外设DMA通道设置回退(暂时释放DMA总线)。如当通道2需要与Memory进行数据传输时,先向DMA控制申请总线使相应通道2的REQ信号有效,若DMA控制器允许通道2进行数据传输,则向通道2响应ACK应答信号。当通道2传输完,DMA控制回退长度的寄存器设定的值进入回退阶段,若数据传输完成,则使REQ信号无效,否则继续使REQ信号有效,并在回退期后当DMA总线空闲时参于DMA总线竞争。在总线空闲时只有不处于回退期间的最高优先级的通道才能获得DMA总线使用权,对Memory进行读写。

经过Design Compiler逻辑综合,DMA控制器在SMIC0.18μm的工艺下,能够达到AHB时钟域90MHz。能满足所设计SoC系统时钟的要求。

2.4 2种架构性能对比

在图1所示架构中,每次DMA传输都要发起1次读与1次写操作。若在DMA传输期间有需要紧急处理的异常响应,AHB总线此时又被DMA控制器占用,则处理器只能等DMA控制器释放AHB总线后才能占用AHB总线进行操作,影响处理器效率与系统对异步事件的响应速度。

图2中是通过DMA控制器的一个通道与Memory相接。DMA控制器包含2个AHB的slave接口,一个是用来对DMA控制器的内部寄存器进行配置,而另一个是被处理器用来对Memory进行读写。首先处理器可以利用Cache中的指令与数据来运行,若出现没命中的问题,也可以对AHB总线上其他存储区域进行访问,因为此时AHB总线没有因DMA传输而被占据。并且除处理器通道外,对于其他所有通道的DMA传输都可以设置回退,

从而使处理器在外设DMA传输期间尽快获得DMA总线,对挂接在DMA控制器上的Memory能尽快进行读写,从而提高处理器的效率。当异常中断发生时,处理器也能尽快对响应中断,提高系统对异步事件的响应速度,从而提高系统的实时性。这样的架构在一定程度上解决了上述架构所产生的影响处理器效率的问题。

3 总结

通过对2种不同架构的分析得出,包含双从AHB接口DMA技术的SoC系统架构,不仅解决了外设与Memory间的大批量数据传输问题,同时又解决了因DMA技术的引入而带来的处理器对异步事件响应速度过慢及处理器效率变低的问题,提高了对异常中断的响应速度,使系统更加适用于硬实时系统。

- LT3751如何使高压电容器充电变得简单(08-12)

- 三路输出LED驱动器可驱动共阳极LED串(08-17)

- 浪涌抑制器IC简化了危险环境中电子设备的本质安全势垒设计(08-19)

- 严酷的汽车环境要求高性能电源转换(08-17)

- 适用于工业能源采集的技术 (08-10)

- 单片式电池充电器简化太阳能供电设计(08-20)