高密度可编程FIFO存储器在视频图像中的应用

个帧必须同时从不同的队列同时。因此,我们的应用需要至少八个队列。

(ii)分离和重传:

有可能从一个标准的FIFO曾经读过的数据又从FIFO丢失了。FIFO指针可以重新编程,允许任何帧都可以根据需求多次读出。

图4显示了赛普拉斯CYFX072VXXX HD-FIFO的框图。

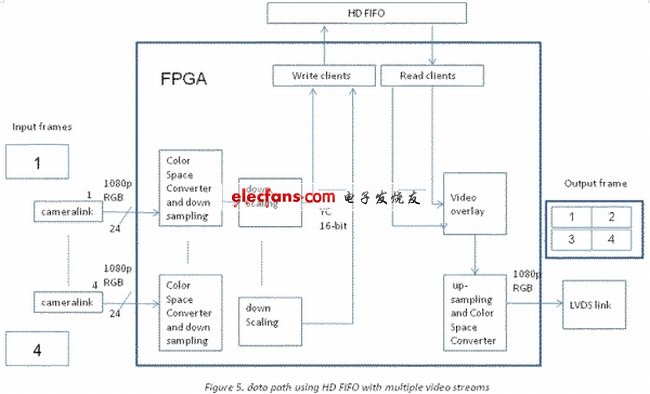

图5给出了使用赛普拉斯HDFIFO替代DDR2芯片的应用案例。

离散HD-FIFO相对于传统实现的优势:

结构优点:

(i) 由于读和写路径是分开的,没有其它操作开销,操作频率可以降低一半以上,这些都是很显著的优势。

(ii)由于使用的是SDRAM控制器,不需要仲裁机制,FPGA内部逻辑变得更简单。

(i) 信号开关频率降低一半以上,允许增加建立时间余量,相对于DDR2来说没有严格的输出同步要求。

(iv) 设计里时钟域的数量减少了,因此降低了相关时序切换和交叉时钟域的问题。

电气优点:

(i)减少了信号切换频率,从而减少了线路板上的开关噪声。

(ii) HD-FIFO 的IO逻辑可以是任何LVCMOS接口,相对于DDR2 SDRAM的SSTL2逻辑有更大的噪声冗余。

节省成本:

在高端FPGA的解决方案中使用HD FIFO可以节省 FPGA资源,具体如下:

(i) SDRAM控制器,降低了所需的存储器,I/O,和逻辑

(ii)视频处理功能,这些功能可以采用多队列特征在HD FIFO上实现,如:

a. 视频信号的隔行/去隔行

b. PIP实施

c. 交叉信号处理

使用高密度FIFO可以节省逻辑元件,寄存器,内存和I / O,可以帮助开发人员把高端FPGA换为更小的FPGA,从而可以节省20 ~ 30%的成本。

Figure6.有无高密度FIFO系统框图比较。

高密度FIFO基于SRAM技术,为客户提供了高数据可靠性和低延迟性。简单易用的总线接口可以减少实施和调试工作。高密度FIFO密度可以达到144 Mb,速度可以到150 MHz,具备segment特色,还有很多增值功能,如多队列和可选的存储器架构,可以帮助开发人员设计更快、更有效率,从而使其适应广泛的应用。它已经是一个成熟的解决方案,可以加速推向市场的时间,同时减少相关设计工作。该器件还可提供很宽的扩展选择,可以适应视频广播,军事,医学影像,基站(网络)设备,满足很多应用,如:

普通高清格式帧缓存 (720p ,1080i ,1080p): 存储四个1080p分辨率的帧

HDTV/SDTV帧同步

交换或格式转换器盒子

高端数码摄像机

军事雷达中高密度缓存

医学成像

基站--3G,4G及网络

- 基于单片机的可编程直流稳压电源设计(08-17)

- 利用可编程电源平衡输入纹波电流的解决方案(09-11)

- 可编程电源设计(01-12)

- NXP (Freescale) i.MX7 96Board(05-17)

- 可编程逻辑控制器(PLC)基本操作及功能简介(03-07)

- 人工智能技术的进程能否加快,可编程芯片才是关键(09-07)