基于DS89C450的Xilinx PROM在系统编程设计

可编程逻辑器件(FPGA、CPLD等)广泛用于现代电子设计中,在一个系统中往往会用1片以上的可编程逻辑器件。作为最大的供应商之一,Xilinx公司的器件获得了广泛的应用。基于查找表技术的FPGA在应用时需要外置一个非易失性存储器来存储配置数据。如何方便灵活地对一个系统中多片FPGA的配置数据进行升级是本文讨论的问题。

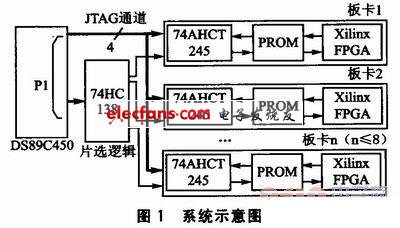

1 系统概述

Xilinx的Platform Flash PROM包括XCFxS和XCFxP系列,它们都是带JTAG接口的PROM,都支持JTAG ISP Programming,本文主要以XCF-01S为例。DS89C450型单片机是一款超高速的高性能单片机,其显著特点是速度快,一个机器周期只需要一个时钟周期;通过使能,可以激活其内部的1 KB数据存储器,来作为数据缓存;同时它具有64KB的内部程序存储器,支持ISP、IAP。

本设计主要实现的功能是:

①DS89C450的在应用编程(IAP)。通过使用IAP,单片机用户代码的更新和修改将十分方便。

②使能DS89C450内部1 KB数据存储器,在对Platform Flash PROM编程时,作为数据缓存,这样将无需在片外扩展数据存储器,从而减小了电路板面积,同时提高了访问速度,节省成本。

③用DS89C450的P1口的4根线模拟JTAG的时序逻辑,实现与Platform Flash PROM的通信;余下的4根线用来构造片选逻辑,将整个电路设计在背板上,将串口引出到设备面板来与上位机通信。

④采用汇编语言开发,使iMPACT下载和单片机下载互不冲突,方便实现插板式机箱结构。

该设计在设备调试、远程维护、功能扩展和修改等方面将具有很高的灵活性,系统示意图如图1所示。

2 DS89C450 IAP的实现

DS89C450内部集成了64 KB的Flash程序存储器,64 KB Flash分为2部分,低32 KB区(地址范围0000H~7FFFH)和高32 KB区(地址范围8000H~FFFFH)。只有高32 KB区才可以由IAP程序访问,这个空间将存放用户代码。DS89C450内部有一个存储器管理单元(MMU),它实际上就是一个状态机,独立于处理器核心而存在,只需向相应的特殊功能寄存器中写入命令、地址、数据等,将启动MMU,实现对高32 KB区的擦除、编程、校验以及系统复位。而在低32 KB区存的是IAP程序,IAP程序代码是通过烧录器烧写进去的。

IAP程序将通过串口和上位机通信,在系统上电后,上位机发出是否要更新高32 KB区代码的命令,若不更新,则IAP程序立即跳转至8000H处取指令,执行高32 KB区的用户代码;若上位机发出了更新高32KB区代码的命令,IAP程序将进入工作状态,它将首先擦除高32 KB区,然后准备接收新的用户代码(即对Platform Flash PROM操作的代码),收到新代码数据之后,将其写入高32 KB区;新代码文件全部写入之后,由上位机发出校验命令,IAP程序将高32 KB区按字节读出,并计算出累加和,作为校验和回送上位机。

上述所有操作都是通过读写2个特殊功能寄存器来实现的,这2个寄存器是FCNTL(地址:D5H)和FDATA(地址:D6H),图2给出了编程的流程。

3 DS89C450片上1 KB数据存储器的使用

无论是在IAP程序更新高32 KB区的用户代码时,还是在刷新Platform Flash PROM内的配置数据时,在DS89C450和上位机之间都会有大量的数据传递。DS89C450内部集成了1 KB的数据存储器,它将用作数据的缓存,因此不需要再扩展外部数据存储器。同时,采用汇编语言开发,将有效提高资源的利用率。这1 KB数据存储器在默认情况下是不可用的,需要设置相应的特殊功能寄存器位来激活。将DME0位(PMR.0)置1激活它,激活之后采用MOVX指令访问,相比访问外部扩展的数据存储器速度更快。

4 DS89C450与Xilinx Platform Flash PROM

结合Xilinx的器件,先简要介绍JTFAG接口的工作原理。

JTAG又称为边界扫描(boundary scan),是符合IEEE STD 1149.1的通信标准,它含有一个TAP控制器,也就是一个状态机。所有的指令、数据的输入以及数据的输出都是在状态机的控制下完成的,如图3所示。

JTAG接口一般用到了下面4根线:

TMS——模式选择输入,在TCK的上升沿送入TAP控制器,用于状态的转换;

TDI——输入引脚,指令和数据通过它在TCK的上升沿送入TAP控制器;

TDO——输出引脚,数据在TCK的下降沿由此输出;

TCK——输入时钟,为TAP控制器的输入和输出提供时序控制。

TAP控制器含有1个指令寄存器和若干数据寄存器(数据扫描链),对于Xilinx的可编程逻辑器件,其指令寄存器一般为8位。TAP控制器的工作流程是,通过TMS引脚,使状态机按照图3所示的转换图处于某一状态下,送入特定的指令

- Xilinx Kintex UltraScale 一半尺寸的 PCI Express 平台 (HTG-K816)(06-15)

- Xilinx全新参考设计提供业界首个单芯片400G解决方案(02-12)

- Xilinx用于工业自动化的机器视觉解决方案(11-30)

- Xilinx多协议机器视觉摄像机参考设计(12-01)

- 机器视觉技术原理解析及解决方案集锦(02-06)

- 机器视觉在汽车电子方向的应用解决方案(02-13)