SOC的高速数据流加密传输的方法实现

SOC的高速数据流加密传输的方法实现

计算机技术的发展使移动存储设备代替纸张逐渐成为信息传递的主要方式,无纸化办公也逐渐成为行业用户的主要办公方式。随着电子商务、数字管理以及移动办公等现代行业的迅猛发展,行业用户(政府、企业、*、涉密机关)对安全通讯及移动存储设备的数据安全要求越来越高。

但是,移动介质存在着众多安全隐患,数据的随意拷贝、数据的任意打印、移动介质的丢失等均能导致信息的泄密或被盗;*、黑客的入侵使网际信息传输完全暴露在不法分子面前。因此,如何保证信息保存及传递的过程中的数据安全,成为安全通讯和移动存储设备重点需要解决的问题。安全移动存储设备替代普通移动存储设备的趋势越来越明显。

目前市场上针对安全移动存储、安全通讯方面的数据流加密设备主要采用软件加密或数据分段加密的方法。这些方法安全度低,很容易被攻破,非常不适合政府、*、涉密机关和企业等安全度要求高的行业用户对重要数据的携带、保存和传输。另外一种安全移动存储设备的解决方案安全度比较高,但是其采用的是CPU实时搬运数据的方法。这种方法虽比前一种方法安全,但是其速度大大降低,仅为400KBps,远远满足不了移动存储设备对20MBps的速度要求。为满足相关领域大批量高速实时加密的市场需求,很多科研单位和企业都在力求解决这一问题。

高速数据流实时加密方法的技术实现

本文介绍一种高速数据流实时加密方法。该方法利用一颗芯片内的硬件模块完成数据的加密和高速传输的功能,安全度更高,传输速度更快。

该芯片架构摒弃了传统的数据进出均由CPU控制的管理方式,而是采用SOC芯片中的硬件模块实现加密、传输的过程,每一个步骤均由专门的硬件模块负责。专用算法模块完成对数据流的快速加密,高速的传输接口完成数据的传输,使大批量数据能真正地、安全地流动起来。加密的同时在高速传输,从而实现了对数据流的实时加密传输,满足安全移动存储、安全通讯等领域对速度和安全性的需求。

1.安全数据流传输

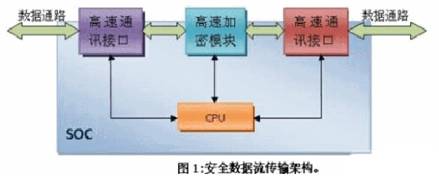

实现高速数据流加解密的前提是采用高速的通讯接口和高速的加解密模块(如图1),完成数据包的接收、加密/解密、发送的过程。高速接口采用双端口的方式,具有同一个流动方向,接收和发送分离(高速接口可为USB2.0、SATA、PATA、以太网等接口)。高速加解密模块可采用安全等级比较高、执行速度比较块的算法,例如DES。

从图1可见:数据流从高速通讯接口流入芯片,经过高速加密模块后,通过另外一个高速接口发送出去,完成一个高速加密通讯的过程。

2.Pipe line数据处理

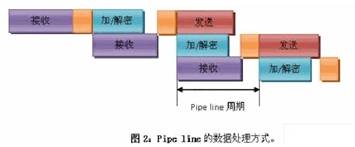

虽然采用高速的通讯接口和高速加密模块,但是每一个数据包在完成接收、加密/解密、发送这三个步骤时,都会占用一定的时间,如果采用顺序执行,这类产品的速度要比没有加密功能的产品降低很多。为再次提高加密传输速度,在数据加密传输的过程中采用了Pipe line(流水线)的数据处理方式(图2),可使处理速度再提高两倍。

处理一个数据包时将整个过程分解为3个部分:接收、加/解密、发送。CPU在每完成一步时仅对这3个模块进行控制,不做数据处理。当大批数据需要处理时,每个时间周期内可同时完成3个数据包中的其中一个步骤,如图2所示,即平均一个时间周期处理一个数据包,该时间周期即为Pipe line周期。但在一个周期内必须保证3个步骤全部执行完毕,CPU才可以对这3个模块进行控制。

由图2可见,Pipe line数据处理周期为:

Tperiod = (Max(Ttx,Trx,Tsec)+Tsys)

在此过程中,如果3个阶段的处理时间相近,处理周期明显减少为原来的1/3左右,一个周期处理一个数据包,速度提高2倍。CPU仅承担控制的任务,并不负责数据的搬运,程序量非常少,这样便大大减少了CPU执行程序所占用的时间。

3.数据存储域的切换

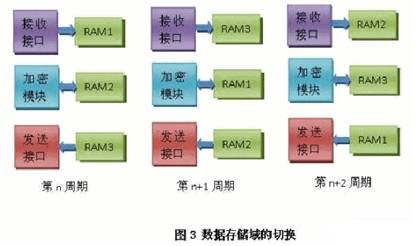

如何保证一个处理周期内可同时对3个数据包分别处理呢?本文采用了数据存储域切换的方法。如图3所示,每个功能模块分别对应一个RAM模块,在第n个周期,接收明/密文并存放在RAM1内;在第n+1个周期,将RAM1切换对应到加/解密模块,将RAM1中的数据包加/解密;在第n+2个周期,将RAM1切换对应到发送模块,并将RAM1中的密/明文发送出去,完成同一个数据包的处理过程。

为实现Pipe Line的流水线工作方式,在同一个周期内,同时处理3个数据包。在第n个周期接收数据到RAM1,加/解密RAM2中的数据,并同时将RAM3中的数据发送出去;在第n+1个周期中,RAM1切换到加/解密模块,RAM2切换到发送模块,而RAM3切换到接收模块,这3个功能模块再分别对相应的数据进行处理,以保证平均一个处理周期处理一个数据包,实现pipeline的流水线工作方式。

该实现方法借鉴了CPU执行指令时流水线作业的方式,并使用2个高速的通讯接口,从而保证数据流上的每一时刻每一个模块都在工作。这种方法可以最大限度地利用所有模块资源,大大提高数据流加密的速度,使实时加密通讯和高速加密存储成为可能。

技术亮点

高速数据流加密的实现方法有下面几个技术亮点,可满足实时、高速、安全的需求。

(1)加/解密和数据传输完全由芯片实现,依靠的代码量非常少,硬件实现比软件实现的速度要快十几倍甚至几十倍。

(2)在SOC内部采用Pipe line的流水线架构,使得在同一个周期内并行执行3个模块,同时完成3个任务,大大缩短了一个数据包的平均处理时间。

(3)改变了CPU传统的管理方式,其仅作为加密模块和通讯接口的控制端,而不在数据搬运的通路上,避免因CPU执行冗长的代码时占用过多的时间。

(4)2个高速的通讯接口使接收和发送分开,同一时间可以接收一个数据包并发送另外一个数据包。

(5)内部集成高速的高安全度的加密算法,使数据以密文的形式在通路上出现,保证数据的安全。

通过实际检测并将该方法与传统加密方法进行对比测试,可明显看出采用此方法实现的数据流加密,其速度比传统的方法提高了50倍甚至更高,有效解决了在通讯、移动存储中加入安全度高的加密算法后速度明显降低的问题,为实现高速数据流加密、高安全性的加密存储设备以及安全通讯设备提供了可靠的硬件和技术保障。

soc 相关文章:

- DE0-Nano-SoC 套件 / Atlas-SoC 套件(10-30)

- 高压电池组监视器可实现先进的电池系统(10-14)

- 如何最大化延长即使具有老化电池的汽车电池组运行时间(08-14)

- 高准确度 60V 电量计如何测量电量?(09-12)

- Cypress电容式触控元件出货量突破10亿颗(08-14)

- 瑞萨电子3大ADAS检测系统解决方案简述(02-08)