利用FFT IP Core实现FFT算法

3 硬件设计

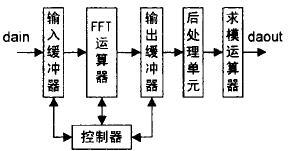

图1整体原理图

设计的整体原理图如图1所示。输入和输出缓冲器分别存储预处理数据和FFT转换结果;FFT运算器负责FFT运算;控制器为输入和输出缓冲器提供读写地址,并控制FFT运算的时序和缓冲器的读写操作;后处理单元从单路复数输入频谱数据中分离出两路实数输入频谱数据;求模运算器实现CORDIC算法,求取转换结果的平方根。设计的输入为两路实数序列,一路作为实部,另一路作为虚部,由连续的256点的数据段组成;输出是间断的256点数据段,各数据段的前128点为第一路的频谱数据,后128点是第二路的频谱数据。根据FFT频谱关于中心点对称的结果,只截取前半段频谱数据并不会丢失任何信息。

整个系统的工作时序为:

①数据以5MHz的速率输入到输入缓冲器;

②FFT运算器以40MHz的速率从输入缓冲器中取数进行运算;

③FFT运算结束时,将转换结果存入到输出缓冲器中;

④输出缓冲器数据以20MHz的速率被送到后处理单元进行转变;

⑤数据被送到求模运算器,进行CORDIC运算,输出;

⑥当③结束时,FFT运算器又回到起始状态,等待处理下一组数据,从而使运算周而复始地进行。整个设计由控制器严格控制。

输入和输出缓冲器由FPGA内部的RAM实现,这些都相对简单。下面重点介绍。FFT运算器、控制器、后处理单元和求模运算器。

3.1 FFT 运算器

FFT运算器采用FFT Core实现,其引擎结构为双Single-output,I/O数据流采用突发(Burst)方式。FFT Core采用Atlantic Interface协议,输入

接口视为主接收器,输出接口视为主发送器。具体接口定义如表1所示。

| 信号 | 方向 | 描述 |

| clk | 输入 | FFT系统时钟信号 |

| reset | 输入 | FFT高有效同步复位信号 |

| master_sink_dav | 输入 | 主接收器数据有效信号 |

| master_sink_ena | 输出 | 主接收器写使能信号 |

| master_sink_sop | 输入 | 输入数据包起始位指示信号 |

| inv_i | 输入 | 转换方向控制信号 |

| date_real_in[M-1...0] | 输入 | 输入实部数据 |

| data_imag_in[M-1...0] | 输入 | 输入虚部数据 |

| fft_real_out[M-1...0] | 输出 | 输出实部数据 |

| fft_imag_out[M-1...0] | 输出 | 输出虚部数据 |

| exponent_out[5...0] | 输出 | 有符号数据块指数 |

| master_source_dav | 输入 | 子接收器接收有效指示信号 |

| master_source_cna | 输出 | 主发送器使能信号 |

| master_source_sop | 输出 | 输出数据包起始位 |

| master_source_eop | 输出 | 输出数据包结束位 |

具体的工作流程:系统复位后,数据源将master_sink_dav置位,表示有采样数据等待输入;作为回应,FFT Core将master_sink_ena置位,表示可以接收输入数据;数据源加载第一个复数数据,同时master_sink_sop置位,表示输入数据块的起始;下一个时钟,master_sink_sop被清零,输入数据按照自然顺序被加入。输入数据达到256点时,系统自然启动FFT运算。通过inv_i信号的置位/清零可以改变单个数据块的FFT转换方向,inv_i信号必须和master_sink_sop信号严格同步。当FFT转换结束时,子接收器已经将master_source_dav信号置位,表示子接收器可以接收FFT的转换结果;同时,master_source_ena信号置位,FFTCore按照自然顺序输出运算结果;在输出过程中,

master_source_sop和master_source_eop信号被置位,表示输出数据块的起始和结束。详细的描述参见文献[4]。

3.2 控制器与后处理单元

控制器大体可分为三个部分:输入缓冲控制(c_i)、FFT运算控制(c_f)、输出缓冲控制(c_o)。c_i为输入缓冲器提供读/写地址和相应的读/写

控制信号;c_f为FFT运算器提供控制信号,严格控制FFT Core的工作时序;c_o为输出缓冲器提供读/写地址及读/写控制信号。控制器通过VHDL语言编程的状态机方式可以轻易实现。

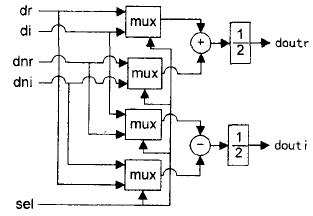

后处理单元其实是式(2)和式(3)的硬件实现,具体的原理如图2所示。

图2后处理单元原理图

图中标识"mux"、"+"、"-"、"1/2"分别表示选择器、加法器、减法器和除法器,dr、di、dnr、dni分别与式(1)和式(2)中的Zr(k)、

Zi(k)、Zr(N-k)、Zi(N-k)相对应。当sel等于0时,提取第一路实序列的频谱数据G(k),实现式(1)功能;当sel等于1时,提取第二路实序列的频谱数据,实现式(2)功能。

3.3 求模运算器

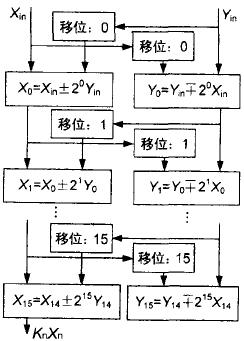

由于工程只要求求平方根,不涉及角度的计算,因此,CORDIC的角度计算部分没有给出,但这并不会影响到幅度的计算。整个CORDIC采用全流水线结构,设计总共有16级流水线单元,各流水线单元结构相似。CORDIC流水线结构如图3所示。

图3 CORDIC流水线原理图

该结果并不是最终结果,还要加一级幅度校正,以去除畸变因子的影响。

- cordic算法verilog实现(简单版)(02-11)

- cordic算法verilog实现(复杂版)(02-11)

- 用CORDIC IP产生SINE波形(02-11)

- FPGA基于CORDIC算法的求平方实现(02-11)

- 基于FPGA的可扩展高速FFT处理器的设计与实现(04-25)

- 教你用示波器频域方法分析电源噪声(02-19)