多功能存储器芯片的测试系统设计方案

时间:07-15

来源:EEFOCUS

点击:

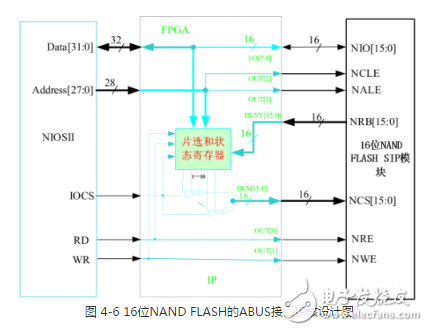

据就是对NAND FLASH地址寄存器的写操作。

验证与总结

将写好的FPGA程序和调试的C代码写入FLASH后,掉电重配置FPGA,串口的输出能正常识别所有设置好的存储器芯片,并能够进行准确地读写功能测试。达到了设计目的。

本文介绍了一种低成本、简单、灵活的多种存储器芯片测试系统的硬件设计,并采用FPGA、FLASH、SDRAM、RS232电路等实现。采用这种方案,用户可根据市场需求,灵活的增加测试系统功能,实现更多的存储器芯片测试。

- 多层板中间地层分割处理技巧(10-23)

- 电子负载在开关电源测试中的应用(10-21)

- 基于硬件架构和软件控制的便携式设备智能电源模块解决方案(02-14)

- 用于高压浪涌保护装置测试设备的设计(03-06)

- LED可靠性测试方案(03-06)

- 告诉你如何看懂电源测试项目(05-29)