如何利用FPGA进行时序分析设计

。。因此对于△T尽量避免,采用同步单时钟,并且尽量采用全局的时钟信号,这样△T几乎为0,,△T的影响几乎不存在,可以忽略不计。

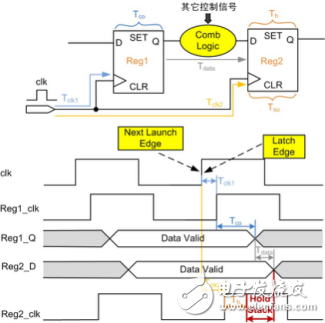

如果保持时间的裕量Hold Stack小于0,则不满足保持时间,也就会产生不稳定态,并通过寄存器传输下去。

图 8 保持时间时序分析图

五、DT6000S项目实例

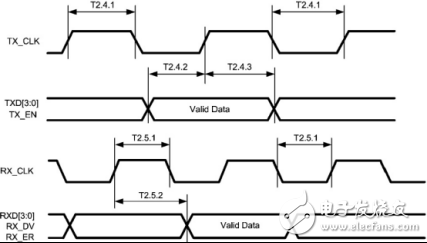

DT6000S项目上有4路光以太网接口连接到FPGA,由FPGA进行实现MAC层和解码IEC61850的SV和GOOSE。以太网PHY通过MII接口和FPGA,因此FPGA与外部的接口有4路MII接口。项目初期是实现1路光以太网接口,并且验证功能正确之后,但是后期变成的4路光以太网时,总会存在1路光以太网通信不正常。经过分析得到是FPGA通MII接口和PHY的时序不满足。如图 9所示为MII接口的时序图,时序不满足分为TX_CLK和RX_CLK。

其一是PHY输出的TX_CLK和FPGA依据TX_CLK产生的TXD[3:0]&TX_EN延时大,主要延时为内部逻辑的延时,PCB延时小并且一致,导致PHY的TX_CLK的建立时间不满足,从而导致发送数据错误。

其二是PHY输出的RX_CLK和RXD[3:0]&RX_DV&RX_ER到FPGA内部同步触发器的延时之差太大,导致FPGA内部同步触发器的RX_CLK的建立时间不满足,从而导致接收数据错误。

因此FPGA在综合时需要添加约束,使之时序满足要求,约束的条件为TXD[3:0]和TX_EN的输出延时要少。RX_CLK和RXD[3:0]&RX_DV&RX_ER路径延时之差要小。添加约束之后,4路MII接口的光以太网数据通信就正常了。

图 9 MII时序图

这里阐述了时序分析基础,说明概念的同时进行了时序分析,通过时序分析理解建立时间和保持时间。希望大家阅读本文之后可以对FPGA时序分析有进一步的了解。

- FPGA设计:时序是关键(07-15)

- SOC时序分析中的跳变点(08-15)

- 基于GAL的I2C总线时序模拟(02-27)

- 输出跟踪和时序控制帮助提高FPGA可靠性(06-22)

- 初学FPGA, 怎么从硬件上理解?(07-25)

- 在进行时序分析时为什么CPR操作得出的效果却是相反的?(02-07)