主流DSP存储器测试方法学习指南:TI KeyStone

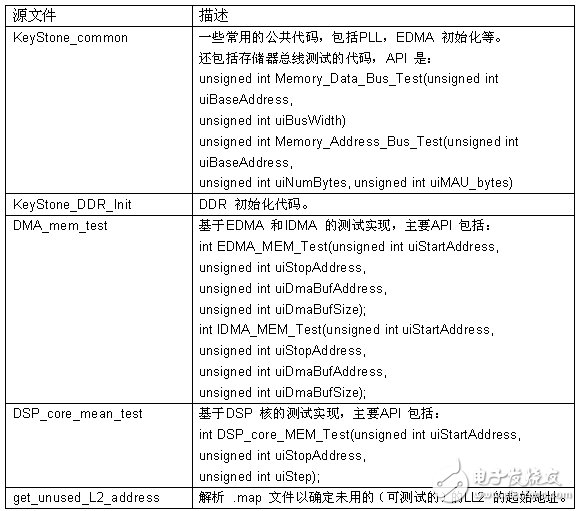

工程文件在"Memory_Test"目录中。一些通用的初始化代码,如PLL, EDMA, DDR 的初始化在"common"目录中。主要的测试代码在"Memory_Test\src"子目录中。表2 描述了主要的源文件。

表2 例子代码的源文件

测试流程由"mem_test_main.c"中的代码控制。基本流程如下:

Disable all caches

Test LL2 bus

Test SL2 bus

Test DDR bus

Test Local L1 with IDMA

Test other core’s L1 with EDMA

Enable 32KB L1P cache

Test Local L2 with DSP core

Test other core’s L2 with DSP core

Test Shared L2 with DSP core

Test 1KB of external memory with DSP core (just cover the data path)

Enable 32KB L1D cache

Test Local L2 with EDMA

Test Local L2 with DSP core

Test other core’s L2 with EDMA

Test other core’s L2 with DSP core

Test Shared L2 with EDMA

Test Shared L2 with DSP core

Test external memory with EDMA (cover full external memory space)

Test 64KB of external memory with DSP core (just cover the data path and L1D cache)

Enable 256KB L2 cache

Test other core’s L2 with DSP core

Test 512KB external memory with DSP core (just cover the data path and L1D, L2 caches)

Test Shared L2 with DSP core through remmapped noncacheable nonprefetchable window

本文选自电子发烧友网6月《智能工业特刊》Change The World栏目,转载请注明出处!

4.2 测试配置

测试代码中有多个宏参数可以用来对测试进行配置。

数据测试填充的数值在"DSP_core_mem_test.c"中定义如下。用户可以在这里添加,删除或修改填充的数值。

unsigned long long ulDataPatternTable[ ] = {

0x0000000000000000,

0xffffffffffffffff,

0xaaaaaaaaaaaaaaaa,

0x5555555555555555,

0xcccccccccccccccc,

0x3333333333333333,

0xf0f0f0f0f0f0f0f0,

0x0f0f0f0f0f0f0f0f,

0xff00ff00ff00ff00,

0x00ff00ff00ff00ff

};

本文介绍的三个主要测试算法可以通用以下在"DSP_core_mem_test.c"和"DMA_mem_test.c"中定义的宏开关使能或禁用。"1"表示使能,"0"表示禁用。

#define BIT_PATTERN_FILLING_TEST 1

#define ADDRESS_TEST 1

#define BIT_WALKING_TEST 1

每个存储器都可以通过"KeyStone_mem_test_main.c"中定义的宏开关控制是否被测试。

#define LL1_MEM_TEST 1

#define OTHER_L1_TEST 1

#define LL2_MEM_TEST 1

#define OTHER_L2_TEST 1

#define SL2_MEM_TEST 1

#define EXTERNAL_MEM_TEST 1

是否用DSP 和或DMA 测试存储器也可以通过"KeyStone_mem_test_main.c"中定义的宏开关控制。

#define TEST_BY_DSP_CORE 1

#define TEST_BY_DMA 1

这个测试工程是在TI 的评估板上实现的。如果要在用户真实的板子上运行,需要根据板子的设计在"KeyStone_DDR_Init.c"中修改相应的DDR 参数。PLL 倍频系数也可能需要在调用KeyStone_main_PLL_init()的代码中修改。

要让这些修改后的配置生效,测试工程必须被重新编译。由于测试工程用到了CSL (Chip SupportLibrary)中的头文件,在重编之前可能还需要重新指定CSL 的包含路径。

4.3 测试时间

测试花的时间主要取决于存储器大小,DSP 和存储器速度。表3 列出了本文介绍的所有存储器测试在TI 的评估板(EVM)上测试所花的时间。

表3 在EVM 板上的测试时间

总线测试花的时间只有几百微秒,而存储单元全空间测试花的时间很多。其中,超过90%的时间都花在对DDR 的测试上。

对存储单元的数据测试,地址测试,和走比特测试所花的时间的比例大概是10:1:64,因为数据测试写读了10 个不同的值,地址测试写读了1 个值,而走比特测试写读了64 个值。

用户可以根据测试时间的要求选用不同的测试用例。一般可能有三种组合:

1. 用毫秒级的时间做简单快速的总线测试。

2. 用秒级时间做全存储器空间的基本测试。测试用例包括总线测试和地址测试。

3. 用几分钟甚至几十分钟做全存储器空间的完善测试,执行本文介绍的所有测试用例。

本文选自电子发烧友网6月《智能工业特刊》Change The World栏目,转载请注明出处!

- Telematics的应用模式与系统设计要领(06-22)

- 西门子SIMATIC系统在安全防爆方面的应用(08-28)

- 低照性能的突破——照亮IP视频摄像机应用前景(11-12)

- TI家用能源显示设备方案(03-12)

- 飞兆、NXP、TI、安森美四家LED驱动方案大比拼(04-07)

- 德州仪器(TI)的电冰箱解决方案(06-10)