如何用低成本的ARM Cortex-M微控制器让家电变得更安全

或异常信号线都会置位。处理器内核将使用一个专用安全中断处理程序处理错误,并关闭家电的电源。第二步,内核可能重启应用(热复位)或停止家电运行,同时显示检修代码。

该解决方案的优势十分明显。B类RAM校验变得完全透明:

· 不影响软件开发方法

· 不必开发某一个微控制器厂商专用的测试程序,只需开发一个在任何情况下都会出现的全局故障处理函数

· 无需专用的RAM分区和链接脚本

· 不占用CPU带宽(校验不会增加存储器读操作延迟)

· 最优的实时性能

最后一个优势是该解决方案在启动时无需进行完整的RAM校验,而且在上电复位后,寄偶校验立即激活,因此降低了引导时间。

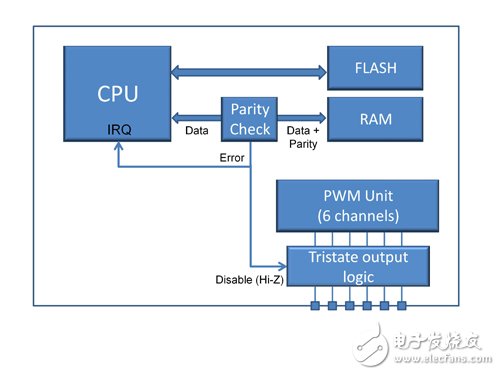

由于拥有高能效、静音运行、高可靠性的特点,无刷电机被广泛用于家电,但是需要复杂的控制算法和专用的PWM外设,需要特别注意故障防护和安全关机。因此,RAM校验机制可提高可靠性和响应性,不是用软件管理安全关闭功能,而是直接向PWM外设发送校验错误信号,自动触发紧急停机功能,避免系统时钟和软件相关的延迟。图3所示框图描述了一个实用的解决方案。

还必须注意系统的其它关键参数。电源监控系统可以设置电压,如果Vdd 电压降至预设电压值,系统将发出一个中断命令。同样,时钟安全系统检查主时钟运行是否正常,如果出现异常,则发出一个中断命令。此外,当发生硬故障、在NMI处理程序内部出现错误或者在引导过程中发生总线故障时,Cortex内核进入锁保护时态,在芯片级提供一个状态显示信号。这三个事件以及校验值合并,产生一个内部紧急关断信号,信号本身与外部断路(break)输入进行或运算。

该标准还需要一个防失效时钟电路。当晶振失效时,时钟安全系统外设(CSS)可自动将主时钟切换到内部高速振荡器,从而实现部分防失效功能。此外,还需要一个通过对比外部预计频率与内部频率来监视外部时钟的方法。实时时钟定时器可由LSI (内部低速)阻容振荡器驱动,以便精确地测量主系统时钟,发现晶体副谐波引起的50%的变化。在系统级,这可节省50/60Hz电网过零检测电路的成本。

该标准提出一个独立的时隙监视方案,防止CPU在程序计数器故障时失控,这是看门狗定时器的职责,多数微控制器均内置看门狗。但是,标准规定看门狗必须完全独立。因此,意法半导体的32位Cortex-M STM32系列微控制器有两个看门狗:第一个窗口看门狗使用主时钟;第二个看门狗使用独立的内部振荡器,通过闪存内的选项字节启动。这种设计可确保在晶体失效时,无论时钟电路配置如何,都能确保至少有一个看门狗在运行。

最后,微控制器还内置一个32位硬件CRC计算器,可大幅加快闪存内容完整性检查,同时将相关CPU负荷(在运行时占用的时间)降至可忽略不计的水平。该外设甚至可以用DMA控制器驱动。在微控制器运行期间,闪存数据完整性检查可在后台进行。

硬件校验长期以来只用于计算机DRAM模块和高可靠性系统。该方法被引进嵌入式市场的通用微控制器,如基于Cortex-M0的STM32F0x产品,随着系统监控和安全功能数量日益增加,该方案可简化产品认证、安全开发的执行,最重要一点是使家电变得更安全。

- 小型低损耗智能集成模块应用方案详解(07-12)

- 采用Cortex-M3单片机设计的WiFi物联网小车(10-27)

- 芯在路上:盘点8位和32位微控制系列(05-15)

- 探索ARM Cortex-M7核心:为明日物联网预做准备(07-23)

- IoT开发者必须关注的6大ARM新IP和技术成果(10-11)

- 为什么说Cortex-M是低功耗应用的首选(06-28)