基于bq24161+TPS2419 双电池供电方案的设计分析

压差V(A-C)可以由RSET 引脚电阻设置,默认典型值为3mV(RSET 悬空)。

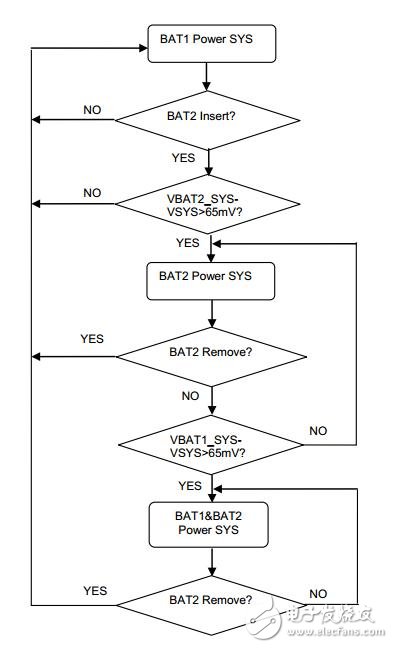

下面在备电突然插入或者拔出的情况下,针对不同的条件对TPS2419ORing 电路的工作原理进行分析,图3 是备电插入、拔出系统供电流程图。

图3 备电插入、拔出系统供电流程图

1) 当主电池给系统供电时,插入备电,如果备电电压满足VBAT2_SYS-VSYS》65mV, 那么备电的TPS2419 会打开外部的MOSFET,备电给系统供电,VSYS=VBAT2_SYS-Vdrop2,其中Vdrop2 是MOSFET 上的导通压降。对于主电的通路来说,如果此时VBAT1_SYS-VSYS 满足关断条件,那么主电池通路的MOSFET 会关断,由备电给系统供电,关断过程中VSYS 电压保持稳定,能够保证系统供电的可靠性。如果VBAT1_SYS-VSYS 不满足关断条件,那么主电的通路的MOSFET 仍然导通,此时主电备电的同时给系统供电。

2) 当主电池给系统供电时,拔出备电,因为此时备电通路MOSFET 没有打开,拔出备电对VSYS 没有任何影响,VSYS 仍然由主电来提供。

3) 当备电给系统供电时,拔出备电。在拔出备电的过程中VSYS 电压会有下降的趋势,当VSYS 电压跌落到主电通路VBAT1_SYS-VSYS》65mV 的导通门槛时,主电回路的TPS2419会迅速打开MOSFET,VSYS 电流由主电池来提供,由于TPS2419 能够迅速打开,因此在整个切换过程中能够保证VSYS 供电的可靠性。

综合以上几种条件下分析,表明本文中TPS2419 设计实现的ORing 电路在备电突然插入或者拔出的情况下,能够完全保证系统供电的可靠性。

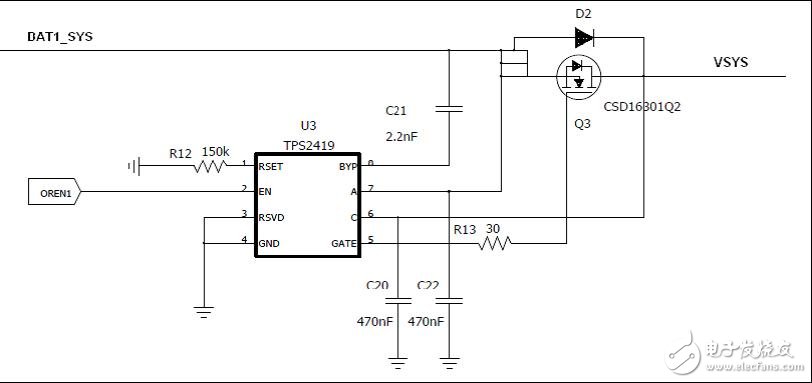

下面先来分析讨论一下主电通路TPS2419 电路的设计,如图3 所示。

图4 主电池通路ORing 电路设计

TPS2419 的A、C 引脚电压检测输入引脚,用来检测外部MOSFET 上的压降,分别连接MOSFET 的源极和漏极,分别连接470nF 的去耦电容。对于MOSFET 的选择要考虑电压等级、Rdson、尺寸、驱动电压等级以及成本等因素。本设计中采用CSD16412Q5A 型N-MOSFET,其VDS 电压等级为25V,RDS(on) 只有13mΩ 。为了最大程度减小对TPS2419 内部电源的干扰,BYP 引脚需要连接一个2.2nF 的去耦电容。GATE 引脚提供外部MOSFET 的栅极驱动信号,其强健的驱动能力可以使得TPS2419 在100-200ns 的时间里迅速的关断外部MOSFET,为了防止过快的电流变化对电路的影响,需要GATE 引脚与MOSFET 的栅极之间串联一个10 Ω ~200 Ω的电阻,本设计中选取30 Ω 电阻R13。RSET 引脚是用力设置MOSFET 的关断门槛,如下式:

(2)

(2)

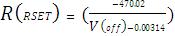

负的关断门槛可以防止由于总线上噪声引起的误关断动作,但也会造成大的反向电流;正的关断门槛可以防止或减小反向电流,但是对噪声的敏感度高, 易在轻载时不断关断、重起。由于本设计是针对电池的应用,输入电源噪声很小,另外负载电流不太大,为了尽量防止反向电流引起的电池之间互充,可以设置关断门槛为0mV,因此取 。

。

EN 引脚为TPS2419 的使能控制,为了最大限度的减小系统待机时候的静态电流,当系统处于待机条件下OREN1 信号拉低,TPS2419 处于不使能状态,静态电流可以维持在最小,此时系统的供电经过肖特基二极管D2 来提供。

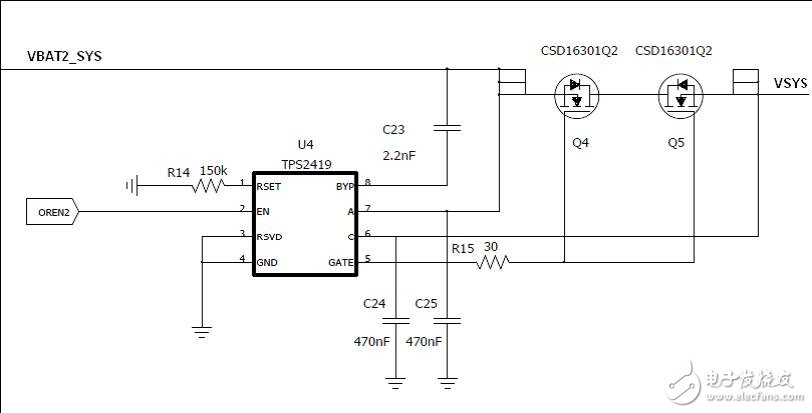

图4 是备电通路TPS2419 电路的设计

图5 备电池通路ORing 电路设计

备电池通路与主电池通路TPS2419 电路设计基本相同,只是MOSFET 管的设计稍有区别。对于相同部分的电流这里不再赘述,只对MOSFET 部分进行分析讨论。如果在应用中需要关断备电池的放电,如果选用单MOSFET 的设计,当OREN2 设置TPS2419 处于不使能状态时,如果备电池电压高于VSYS 时,电流就会从外部MOSFET 的体二极管流向VSYS,从而不能断开备电的放电,因此这里需要采用对管的结构,这样就可以完全切断备电放电的通路。

2.4 实验结果分析

测试电路在静态负载以及动态负载不同负载条件下,系统供电电压VSYS 的稳定性以及VBAT1_SYS 与VBAT2_SYS 之间是否相互影响:

1) 备电不在位,主电提供系统电压VSYS,VBAT1_SYS》VBAT2_SYS 条件下插入备电。过程中不存在主电、备电切换供电过程,测试VSYS 电压的稳定性以及备电对主电通路的影响;

2) 备电不在位,主电提供系统电压VSYS,VBAT1_SYS《VBAT2_SYS 条件下插入备电。过程中系统供电由VBAT1_SYS 切换为VBAT2_SYS,测试在切换过程中VSYS 电压的稳定性以及备电对主电通路的影响;

3) 备电在位,主电提供系统电压VSYS,VBAT1_SYS》VBAT2_SYS,拔出备电。过程中不存在主电、备电切换供电过程,测试VSYS 的稳定性以及备电对主电通路的影响;

4) 备电在位,备电提供系统电压VSYS

- 德州仪器:将主动安全升级为标准配置(02-21)

- 基于DSP和FPGA的机器视觉系统设计与实现(03-07)

- 剖析智能手表内部芯片硬件结构:哪些厂商获益?(03-21)

- TI数字中频芯片GC6016配置与应用分析(04-15)

- 加快TPA2028D1对突发音信号(短暂提示音)的响应(04-10)

- 德州仪器ZigBee单芯片推动物联网应用(05-17)