资深工程师给你讲述DC/DC的设计技巧

"绿色"系统的发展趋势不仅意味着必须采用环保元器件,还对电子产业提出了节能的挑战。能源之星(EnergyStar)和80+等组织都已针对各式消费电子(特别是计算类)颁布了相关规范。对当前的消费者而言,更长的电池寿命也是个十分吸引的特性。因此,更长的电池寿命、更小的外形尺寸及各国政府推出的新法规都在要求必需谨慎选择电源元件,尤其是对板上的DC-DC转换器。这表示着新平台的功率密度、效率和热性能必须大幅提高。

众所周知,设计理想的DC-DC转换器涉及到众多权衡取舍。功率密度的提高通常意味着总体功耗的增加,以及结温、外壳温度和PCB温度的提升。同样地,针对中等电流到峰值电流优化DC/DC电源,几乎也总是意味着牺牲轻载效率,反之亦然。本人结合自己十多年的DC-DC应用经验,谈谈DC-DC转换器的基本原理和设计经验技巧。

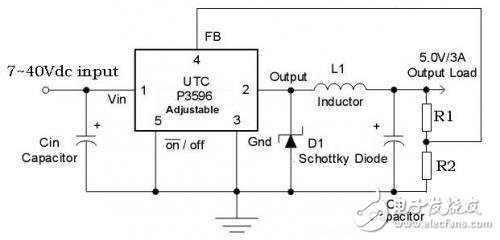

DC-DC就是直流-直流变换,一般有升压(BOOST)、降压(BUCK型)两种。降压式DC/DC变换器的输出电流较大,多为数百毫安至几安,因此适用于输出电流较大的场合。降压式DC/DC变换器基本工作原理电路如图1所示。VT1为开关管,当VT1导通时,输入电压Vi通 过电感L1向负载RL供电,与此同时也向电容C2充电。在这个过程中,电容C2及电感L1中储存能量。当VT1截止时,由储存在电感L1中的能量继续向 RL供电,当输出电压要下降时,电容C2中的能量也向RL放电,维持输出电压不变。二极管VD1为续流二极管,以便构成电路回路。输出的电压Vo经R1和 R2组成的分压器分压,把输出电压的信号反馈至控制电路,由控制电路来控制开关管的导通及截止时间,使输出电压保持不变。

图1、降压式DC/DC变换器基本工作原理电路

DC-DC设计技巧

一.DC-DC电路设计至少要考虑以下条件:

1.外部输入电源电压的范围,输出电流的大小。

2. DC-DC输出的电压,电流,系统的功率最大值。

二.基于以上两点选择PWM IC要考虑:

1. PWM IC的最大输入电压。

2.PWM开关的频率,这一点的选择关系到系统的效率。对储能电感,电容的大小的选择也有一定影响。

3.MOS管的所能够承受的最大额定电流及其额定功率,如果DC-DC IC内部自带MOS,只需要考虑IC输出的额定电流。

4. MOS的开关电压Vgs大小及最大承受电压。

三.电感(L1),二极管(CR1),电容(C2)的选择

1. 电感量:大小选择主要由开关频率决定,大小会影响电源纹波;额定电流,电感的内阻选择由系统功耗决定。

2. 二极管:通常都用肖特基二极管。选择时要考滤反向电压,前向电流,一般情况反向电压为输入电源电压的二倍,前向电流为输出电流的两倍。

3. 电容:电容的选择基于开关的频率,系统纹波的要求及输出电压的要求。容量和电容内部的等效电阻决定纹波大小(当然和电感也有关)。

如何得到一个电源纹波相对较小、对系统其他电路干扰相对较小,而且相对稳定可靠的DC-DC电路,需要对以上电路的原理做如下修改:

1.输入部分:电源输入端需要加电感电容滤波。目的:由于MOS管的开关及电感在瞬间的变化会造成输入电源的波动,尤其是在系统耗电波动较大时,影响更为明显。

2.输出部分:

(1)假定C2的选择的100uF是正确的,我们想得到更小的纹波,可以将100uF的电容改成两颗47uF的电容(基于相同类型的电容);如果100uF电容采用的是铝电解,可以在原来的基础上加一颗10uF的磁片电容或钽电容。

(2) 在输出端再加一颗电容和一颗电容对原来的电源做一个LC滤波,会得到一个纹波更小的电源。

PCB布线时,应注意几点:

1. 输入电源与MOS的连线要尽可能的粗。

2. Vgs也要粗一点,千万不要以为粗细没关系,(注:一般系统功率相对较低时,输出电流不大,粗细的影响不明显)关键时刻会影响电源的稳定性。

3. CR1, L1尽量靠近Q1。C2尽量靠近L1。

4. 反馈电阻的线尽量远离电感L1。

5. 反馈电压的地与系统的地尽量的近,保持在一个电位上。

6. CR1的地线千万要粗,在MOS的打开的时间里,L1的电流是由CR1的通路提供,即由地流向L1。

DC-DC应用技巧

在常见的DC/DC变换器中,有很多的应用技巧是不为工程师所掌握的。 现拿 UTC P3596应用电路来作一个说明,与诸位分享交流:

DC-DC应用技巧一

当我们用这个电路做好 Buck 以后,电感量达到其 Spec. 的要求,却发现负载调整率过低。这种情况下,很多同学都认为芯片品质问题等等。 其实由于芯片的半导体工艺不能使内部的运放的带宽(bandwidth)做的很大。所以我们所做的要么就是屏蔽内部的运放(象我们常见的3

- 为EMI敏感和高速SERDES系统供电(08-17)

- 高可靠DC/DC变换器模块设计(09-15)

- DC/DC转换器的发热问题缘由(10-30)

- 一种CMOS绿色模式AC/DC控制器振荡器电路(09-16)

- 凌力尔特大功率多相同步升压型DC/DC控制器LTC3787(10-15)

- 电动 / 混合电动汽车电池管理系统的可靠性(11-09)