数字电源UCD9224与UCD7232应用中输出电压关机负过冲的分析及解决

摘要

UCD9224 可以与UCD7232 配合设计非隔离数字电源。在某项目中,采用1 片UCD9224 与4 片UCD7232 设计了四相交错并联输出的数字电源,输出规格为1.0V/80A。在测试中发现,关机时输出电压存在严重的负过冲,幅值可达-380mV。经过仔细定位发现,引起负过冲的根因是UCD9224 进入reset 模式后,SRE_1A 和SRE_1B 引脚变为高阻态,其电压有反弹并下降缓慢。基于此,在SRE_1A 和SRE_1B 引脚各设计一颗下拉电阻,可以给上述两个引脚快速放电,彻底解决负过冲问题。本文对定位过程给予了详细的描述和分析,并最终给出了结论。

1. 数字电源系统设计

某非隔离BUCK数字电源系统的设计基于数字控制器UCD9224与驱动器UCD7232,采用四相并联并配置于交错模式,输入电压为12V,输出电压为1.0V,输出电流最大为80A。

1.1 数字电源系统方框图

UCD9224是内部集成ARM7核的非隔离数字电源控制器,可以灵活的配置为多路或多相模式,并带有PMBUS接口。UCD7232则是与UCD9224配合使用的增强型驱动器,与UCD9224之间有多个信号的交互,完成驱动信号接收,电流采样,故障上报等工作。

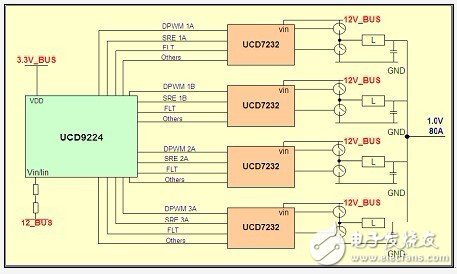

图1所示的是该数字电源系统的方框图,包含有1片UCD9224和4片UCD7232,以及功率 MOSFET,输出电感和输出电容等。该系统有两个输入总线,分别是3.3V和12V,其中3.3V用来给UCD9224供电,12V输入到UCD7232和BUCK转换电路,完成到1.0V的转换。该供电架构区别于传统的3.3V由12V通过LDO转换得来的设计。

图 1:数字电源系统框图

1.2 UCD9224与UCD7232的关键信号连接

UCD9224共有4组关键信号与4片UCD7232连接,分别完成电压转换控制,同步整流模式配置和故障上报等功能,下面是这些关键信号的简单介绍:

1) DPWM:由UCD9224输出到UCD7232,是后级BUCK电路的驱动信号来源。其中, BUCK上管驱动信号与DPWM的逻辑相同,BUCK下管的驱动信号与DPWM的逻辑相反。

2)SRE:由UCD9224输出到UCD7232。当UCD7232的SRE_MODE引脚(图1未示意)上拉至高电平后,UCD7232被配置为同步整流模式。当SRE为高时,BUCK的下管得到相应的驱动信号,该驱动信号由DPWM决定。当SRE为低时,BUCK电路的下管处于关闭状态。

3)FLT:由UCD7232输出到UCD9224。当UCD7232检测到欠压,过流或过温等故障后,FLT引脚变为高,UCD9224识别之后会根据当前配置进行相应处理。

4)CS:由UCD7232 的IMON管脚输出到UCD9224的CS管脚。该信号为输出电流采样信号。

2. 输出电压的负过冲

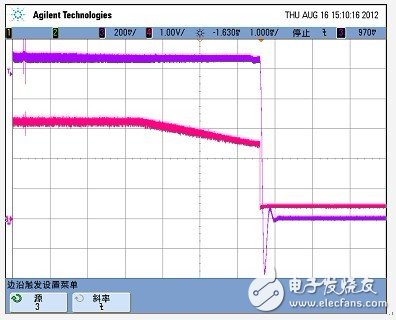

对该系统做输入关机测试时,如果只关闭3.3V,12V保持不变,发现输出电压有明显的负过冲,幅值超过-300mV。如图2所示,关机时输出电压(1.0V,CH3)的负过冲达到了-380mV,测试条件为输出端空载。

3. 负过冲的定位及原因分析

在定位负过冲的过程中,发现关机时BUCK下管的驱动信号异常,进一步发现SRE信号异常,最终发现根因是SRE_1A信号和SRE_1B信号在关机过程中有反弹并且下降缓慢。

3.1 关机时BUCK下管驱动信号异常

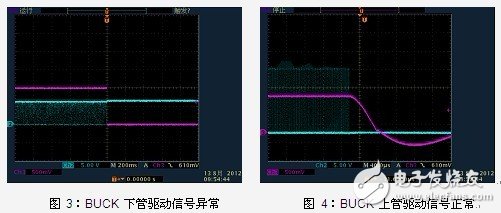

保持输入电压12V不变,当关闭3.3V时,输出电压有很大的负过冲。在空载输出时,输出端亦有负过冲,据此初步判断BUCK下管可能有长时间导通,输出电容电压通过长时间。导通的 BUCK下管泄放到地。而实测试发现,BUCK下管的确如此,如图 3。可以观察到,输出电压下降后,BUCK下管的驱动信号(蓝色线)一直保持为高,时间超过了1s。而BUCK上管的驱动信号(蓝色线)在关机过程中正常,如图 4。

3.2 关机时SRE信号异常

理论分析知,关机时SRE信号会变为低电平,BUCK下管的驱动信号随之也会变为低。而该电源系统关机时BUCK下管的驱动信号一直保持为高,怀疑为SRE信号异常。

实测发现SRE_1B(图5中的CH1;CH2为SRE_MODE信号;CH3为输出电压)在下降过程中出现了反弹,然后缓慢下降。而SRE_2A(图6中的CH1;CH2为SRE_MODE信号;CH3为输出电压)则没有反弹,快速下降到0V。

进一步详细测试发现,SRE_1A与SRE_1B在下降过程中皆有反弹,信号异常;而SRE_2A与 SRE_3A正常。

3.3 SRE 信号异常的原因分析

图7显示的是SRE_1B(CH3),V33D(CH2,3.3V)和BPCAP(CH1,1.8V)在关机时的波形。可以观察到,在SRE_1B出现反弹时,3.3V下降到了2.8V左右,UCD9224进入了reset模式。

图 7:3.3V 与 SRE 信号

根据UCD9224芯片的硬件设计,其供电电压下降到2.8V时会处于reset模式。而其进入reset模式后,SRE_1A引脚和SRE_1B引脚变更为高阻态,SRE_2A引脚和SRE_3A引脚变为低电平态(被 UCD9224强制拉低

- 管理多电压轨系统让数字电源管理变得简单(08-17)

- 数字电源系统管理加快 “绿色”电子系统的上市时间(07-25)

- 数字电源设计与实现问题探讨(08-08)

- 系统设计师的数字电源(09-19)

- 数字回路控制电源转换的设计(01-31)

- 数字电源管理技术及电源管理总线(10-10)