新型多路输出稳压器为FPGA和处理器提供更小、更可靠的电源解决方案

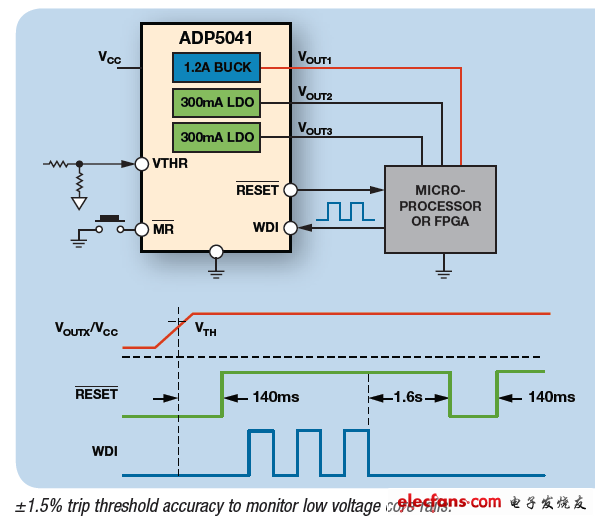

间内微处理器未能使WDI跳变,则说明发生代码执行错误,由此产生的复位脉冲将重新启动微处理器并使其进入已知状态。

除了WDI上的逻辑跃迁外,VCC欠压或/MR变为低电平所导致的复位置位也会将看门狗定时器清零。复位置位时,看门狗定时器清零,直到复位解除置位后才重新开始计时。ADP5041具有一个特殊电路,它能检测WDI引脚上的看门狗刷新输入端施加的三态条件,WDI引脚通常由处理器/DSP输出端口控制。当处理器将此端口设为三态模式时,看门狗刷新定时器禁用,防止看门狗复位处理器。当器件支持处理器/DSP休眠工作模式时,此特性非常重要,此时内核禁用,看门狗定时器无法刷新。此外它还提供丰富的订购选项,可以满足其它常见的复位和看门狗时序要求。

所有集成稳压器都有可选的工厂可编程有源下拉电阻,用于在稳压器被使能引脚、Vin欠压(UVLO)或热关断(TSD)禁用时将相应的输出电容放电。有源下拉电阻确保稳压器关断时,输出电压立即被拉至GND,从而提高系统可靠性,确保输出电容上无残余电压,避免周期供电期间发生闩锁事件。

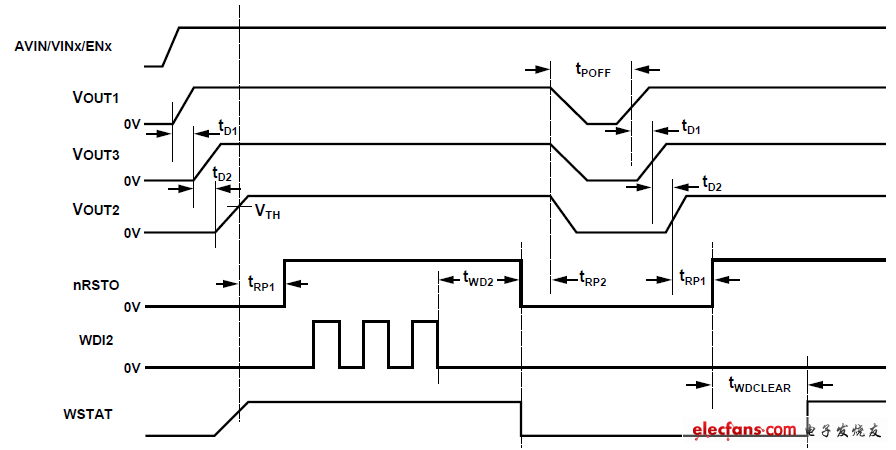

为提高电表等远程系统的可靠性和正常工作时间,该多路输出稳压器集成了另一个看门狗电路,如果系统不能正常工作或正确响应,远程系统可以自动"周期供电"。ADP5042是一款集成两个300mA LDO、上电复位和双通道看门狗定时器的800mA降压稳压器。

看门狗定时器1 (WDI1)监控处理器代码活动,如果因为代码执行错误,WDI1未在规定的时间(1.6s或102ms)内选通,ADP5042的/RESET引脚就会变为低电平并保持规定的时间(24ms或160ms),使处理器进入复位状态,并在处理器复位后离开复位状态。第二看门狗定时器(WDI2)同样监控处理器代码活动,但时间长得多(32分钟、64分钟或128分钟)。如果在规定的时间内WDI2未选通,则说明发生了WDI1(处理器复位)无法解决的故障,因而该多路输出稳压器需要进行完整的周期供电。如果多路输出稳压器发生WDI2超时,则三个输出电压进行周期供电,从而启动系统的完整硬件周期供电,而无需技术人员对系统执行周期供电。由于ADP5042能够对系统进行远程周期供电,因此系统可用性更高,并且可以节省让技术人员手动为系统周期供电的成本。利用WSTAT引脚可以确定系统复位的原因,看看到底是WDI1(处理器复位)还是WDI2(完整硬件周期供电)引起处理器复位。

4: 低噪声解决方案

开关降压稳压器上的专用MODE引脚可以通过微处理器GPIO端口方便地控制,迫使开关稳压器以恒定PWM模式工作。在轻负载下,开关稳压器以突发模式工作会产生宽带噪声,如果受电电路(收发器、ADC、音频)对宽带噪声敏感,那么这种控制就是必需的。集成到这些多路输出稳压器中的LDO具有1.7 V至5.5 V的输入电压范围,配合一个降压稳压器使用时,低输入电压使得LDO能够提供极高效率的低噪声输出。例如,降压稳压器可以用作前置稳压器,实现5V输入到1.8V输出的高效率压降,然后将此1.8V电压施加于LDO的输入端,以提供极低噪声的1.2V输出电压,从而以非常高的效率从5V初始输入为极敏感的模拟电路供电。集成LDO具有高PSRR(即便Vin-Vout裕量较低)和低内部噪声,稳压器之间的串扰已被降至最小。为噪声敏感型电路供电时,所有这些特性都很重要。

- 为EMI敏感和高速SERDES系统供电(08-17)

- 虚拟远端采样控制器惠及视频安保(10-26)

- 固定频率工作的降压稳压器设计(11-23)

- 稳压器的输出电压精度是否糟糕(11-03)

- 汽车稳压器适应极端环境的设计方案(12-30)

- 高功率密度、双通道 8A μModule 稳压器(01-10)