基于FPGA和IP核的数码相框的设计和实现

数码相框作为一种数码消费品和装饰品的结合物,在市场上受到越来越多的关注。目前的数码相框方案多采用MCU为核心的架构,相框功能固定,不便于产品升级。针对以上问题,本文设计了基于Nios II的多功能数码相框,该相册主要包含以下功能:支持包括BMP、JPEG在内的多种常见文件格式的图像显示;图像旋转、缩放、浏览切换等特效;支持图片浏览时背景音乐播放;可通过带FAT文件系统的SD卡进行图像数据更新,同时还具有时间显示等扩展功能。系统中将需要耗费大量时间的复杂操作(如图像解码、图像的各种特效功能以及SD卡控制)用挂载在Avalon总线上的自定义模块实现。缩短了处理时间,提高了系统响应速度。系统采用基于Nios II处理器的SoPC技术,使得该数码相框具有灵活性高、可重配置、便于升级等优点。

1 总体设计

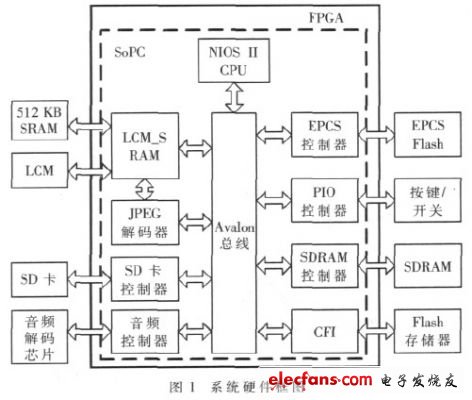

本系统采用经济型的Cyclone II FPGA芯片作为核心,基于Nios II软核处理器,采用软硬件结合的方式设计实现。系统的硬件总体框图如图1所示。

SD卡作为文件存储介质,用于存放音频与图像文件,编写SD卡控制器对SD卡进行读写控制;采用LCM显示屏作为数码相框的显示界面,SRAM作为LCM的显示缓存,存储图像数据供LCM刷新,并由LCM_SRAM IP核控制图像的显示;SDRAM为Nios II软核程序运行空间;EPCS对FPGA进行配置;Flash用来存储软件代码和数据。

2 功能模块设计

根据数码相框所要实现的功能,设计了如下模块:

2.1 LCM_SRAM IP核设计

该模块主要功能是图像数据存储、LCM参数配置以及图像的缩放、旋转、切换效果控制等。以硬件方式实现图像切换效果,提高实时性的同时降低对CPU的依赖。

2.1.1 切换特效实现

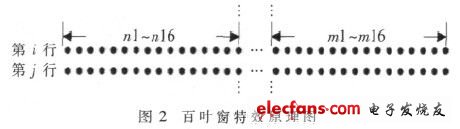

设计中通过控制LCM读取SRAM的地址实现不同的图像切换效果,如上方切入、下方切入、百叶窗、菱形等八种方式循环出现。切换时,LCM上同时存在新旧两幅图像的数据,因此,缓存中需要存储这两幅图像的数据。以百叶窗效果为例,每行以16个像素作为间隔,将LCM的每一行分割成20个条形区域。如图2所示,第i行被分割后,第一个区域的像素点为n1~n16,最后一个区域为m1~m16.每个条形区域中,新图像的数据逐渐向右覆盖旧图像数据,从而形成百叶窗效果。具体实现过程为:在第一次刷新时,每行的各个条形区域的第一个像素点(n1,…,m1)读取新图像的数据,各区域其他像素点(n2~n16,…,m2~m16)仍然读取旧图像的数据;第二次刷新时,每行各个条形区域的前两个像素点(n1、n2,…,m1、m2)读取新图像数据,其他像素点(n3~n16,…,m3~m16)仍读取旧图像的数据。屏幕刷新16次则可实现百叶窗切换效果。图2中每个圆点代表显示屏的一个像素点。

2.1.2 缩放算法实现

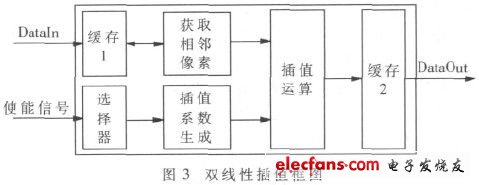

为实现图像缩放功能,该模块实现了如图3所示的双线性插值缩放算法。该算法利用了需要处理的原始图像像素点周围的4个像素点的相关性,通过双线性算法计算实现图像缩放[2]。设计中使用SRAM作为显示缓存,无严格的实时性要求,因此忽略了行场同步信号,简化了模块设计。

缓存1模块是待缩放图像数据的缓存,存放来自SRAM中解码后的RGB565数据。插值系数生成模块的使能信号来自旋转模块或者按键输入,由选择器进行判断,按键按下时,按照设定的行列缩放因子计算行列插值系数;若使能信号来自旋转模块,则根据原始图像的分辨率计算出旋转过后的分辨率,并按照屏幕尺寸确定完整显示该图像能达到的最大分辨率,以此计算行列缩放因子。获取相邻像素模块用来控制缓存1模块的读地址,从SRAM中读取相邻4个像素值。插值运算单元根据相邻4个像素的值及插值系数进行双线性插值运算,并将数据输出至缓存2,缓存2在SRAM空闲时将数据写入SRAM中。

2.2 SD Card Controller IP核设计

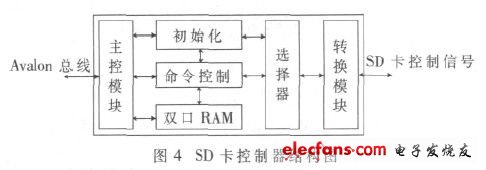

SD卡是一种基于半导体快闪记忆器的存储设备,其数据传送和物理规范由MMC发展而来。系统中将SD卡控制器设计成一个SPI模式的IP核,通过软件驱动实现SD卡的基本读写操作,即不需要复杂的硬件电路又能得到比软件模拟SPI的控制方式更快的读写速度。SD卡控制器结构图如图4所示。

2.2.1 功能模块划分

主控模块的端口与Avalon总线连接,用于缓存SD卡命令,并存储扇区地址、待发送的数据到双口RAM以及从中读取数据等。初始化模块完成对SD卡的初始化操作。命令生成模块完成SD卡命令、参数、命令校验值的发送和命令回执的读取以及数据的收发。串并、并串转换模块的主要作用是实现串并或者并串转换[3]。

使用Quartus II自带的逻辑分析仪(SignalTap II工具)

- 一种消防应急灯具专用控制芯片的设计(11-02)

- 基于FPGA的8段数码管动态显示IP核设计(02-03)

- 基于FPGA和IP Core的定制缓冲管理的实现(08-14)

- 基于Altera ASI IP核的ASI发送卡实现(02-25)

- FPGA的高速多通道数据采集控制器IP核设计(04-22)

- 基于EDA或FPGA的IP保护的实现(09-16)