基于Altera公司EPM240芯片的智能拨号报警系统设计

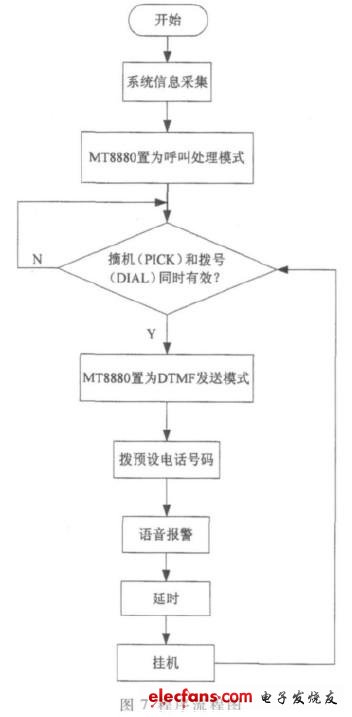

PLD的三个控制模块都是采用VHDL语言编程来实现的[4-5],其中电话信号音检测模块DJF1用来检测公用电话网络传递的语音信号,摘机/挂机控制模块DJF2用来控制摘机/挂机电路,实现电话的接通和关断,DTMF收发时序模块DJF3控制DTMF拨号电路自动拨打预先设定好的电话号码。系统的主程序流程图如图7所示。

系统的工作过程:当红外传感器检测到人体入侵信号EN后,摘机/挂机控制模块启动并产生摘机信号PICK,使摘机/挂机电路进行摘机。摘机后,DTMF收发时序模块将MT8880设置为呼叫处理模式。然后电话信号音检测模块通过对IRQ的计数判别电话音是否为拨号音。如果不是拨号音,则电话挂机,然后再摘机重拨。如果是拨号音,则MT8880设置为DTMF发送模式,同时MT8880拨打预置电话和发送语音报警信号。发出报警信息后延时,电话信号音检测模块检测电话音是否为回铃音。如果是,则延时挂机;如果不是,则挂机重拨。

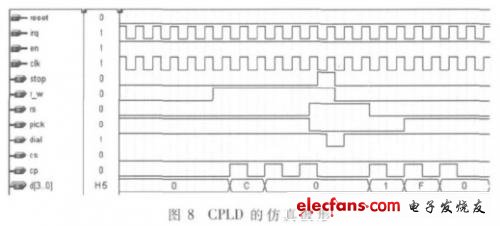

CPLD芯片采用的是Altera公司的EPM240芯片,该芯片具有片内存储器,系统掉电和复位后不用重新向芯片下载程序就能正常工作。系统设计完成后,对三个功能模块进行逻辑编译、逻辑综合及优化、逻辑布局布线、逻辑仿真,然后将生成的配置文件下载到CPLD芯片。将功能模块进行时序仿真验证,仿真波形如图8所示,可以看到功能模块达到所期望的逻辑功能。

本文采用CPLD控制核心实现了智能报警系统。由于利用EDA技术进行系统设计,外围器件少、体积小、功耗低、可靠性高。通过修改VHDL源程序就可以增加一些新的功能,提高了设计的灵活性,具有较好的应用前景。

Altera公司 源程序 VHDL 报警系统 CPLD 相关文章:

- 基于FPGA的洗衣机控制系统的设计与实现(07-27)

- 传授压箱绝技:从SoC设计人员那都了解不到的功耗管理问题(08-04)

- 基于CPLD和VHDL的智能拨号报警系统的设计与实现(02-20)

- 单片机Keil软件仿真与调试技巧(06-03)

- 基于可编程逻辑器件的数字电路设计(10-16)

- 基于Max+PlusⅡ与VHDL的数字电压表设计(08-26)