基于SoPC的SD卡文件系统的设计

SD卡中的数据是以块为单位进行存储的,如果在硬件层面对其进行操作,则不仅要非常了解SD卡的数据存储结构,还要对FAT系统有深刻的理解,然后用复杂的时序状态机对其扇区进行初始化和读取控制,对硬件直接进行操作可以节省FPGA资源。为了更有效地组织和管理SD卡中的数据,必须采用文件的格式进行组织数据,这就要求在SD卡中内嵌文件系统。而随着FPGA的高速发展,以Altera NIOSⅡ和Xilinx的MicroBlaze为代表的软核处理器以其高可定制性、与ARM相比相同价格下的高性能得到广泛的应用。

本文正是利用其丰富的外设和接口定制构建SD卡的FAT文件系统。

1 接口和控制器的设计

1.1 接口的配置

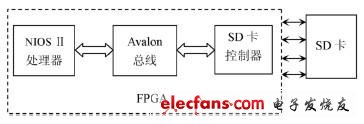

SD卡有SD模式和SPI模式2种,SPI是一种高速、同步、全双工的通信总线,只占用4根信号线,节约芯片的管脚,有利于PCB的布局。前者速度较快,后者比较方便我们采用后者SPI与FPGA进行通信,它由4个信号组成,分别是CS(片选信号)、MOSI(主机到SD卡)、MISO(SD卡到主机)、SCLK(主机和SD卡的同步时钟),以主从方式工作,本文中SPI为主机,SD卡是从机,处于单主单从模式。在由NIOSⅡ软核处理器控制的Avalon总线下可以方便地与SD卡进行对接。Avalon总线是一种将片上处理器和外设连接成片上可编程(SoPC)的一种简单总线结构,它规定了主从设备之间的结构方式及其通信方式,通过使用SoPC Builder可以很方便地将自定义外设和其他组件组合起来,生成按照组件例化的系统模块,并自动生成内部总线逻辑,自动完成外设和存储器的地址映射、中断控制和总线控制。图1所示为设备之间的连接示意图,NIOSⅡ处理器和外设SD卡控制器的通过Avalon总线结构进行数据交换和沟通,SD卡控制器控制着外部SD卡存储介质。

1.2 控制器的设计

SD卡控制器是FPGA和SD卡之间进行通信的翻译官,主要实现3大功能:(1)复位和初始化SD卡。控制器按照SD卡总线协议产生控制时序对其进行复位和初始化。

(2)读写SD卡。控制器通过CMD线发送读或者写的命令以及SD卡扇区地址,确认收到正确的响应后,通过DAT线进行读和写操作(分别涉及串并转换和并串转换),一次传输一个扇区的数据(512B),传输完毕后将就绪信号置为有效。

(3)设置SD卡。通过CMD线发送命令和参数,不发送或接受数据。

图1 设备连接示意图

1.3 SoPC中的硬件搭建

SoPC(SystemonaProgrammableChip),即可编程片上系统,用可编程逻辑把整个系统放到一块硅片上,是一种特殊的嵌入式系统,可以编程的片上系统(SOC)。

借助于AlteraSoPC方便的组件定制、硬件组装和它的灵活的设计方式,不用一个个亲自用硬件语言去实现各个组件,只需要在SoPC里定制,最后结果如图2所示,因为SD卡的工作频率最高为25MHz,与FPGA自身的时钟频率不一定一样,所以要加上clock_crossing用于协调2个不同的时钟域。onchip_memory是片内存储器,用于储存程序运行的代码或者堆栈之类的变量。timer和sysid用来协调这些组件良好运作,例如SoPCBuilder会使用SystemID为每个系统提供识别符号,NIOSⅡEDS可以用此防止使用者烧录与硬件信息不符合的sof文件。Timer是内部时钟定时。如果丢失这两个组件,会导致最后的软件运行出现错误。

图2 SoPC组件定制

其中sd_wp_n是SD卡写保护信号线,由于默认激活SD卡所以片选信号没加。altpll是锁相环,用来调节稳定所需的时钟信号,DE2系列的开发板上都有1到2个锁相环。jtag_uart用来调试、打印数据到控制台,验证读取写入的数据是否相同。

2 驱动程序的设计

SD卡处于SPI模式的驱动主要包含有:(1)SPI底层的操作,SPI的命令和数据块都是以8个比特为单位进行分组和发送的。

(2)关于CMD的操作,主要有SD卡的初始化以及SD卡的读写,先发送命令然后再发送CRC校验。

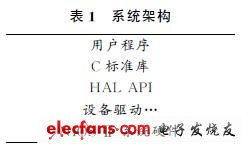

(3)CRC校验使用NIOSⅡ来解决这个问题:NIOSⅡ软件架构建立在硬件抽象层HAL(Hardware AbstractionLayer)之上,HAL为NIOS软件开发者提供了编程接口、底层的设备驱动、HALAPI、和C标准库等资源[6],表1为系统整体的架构示意。

HAL的系统库为NIOSⅡ软件设计人员提供了应用程序与底层硬件交互的设备驱动接口,简化了应用程序的开发。HAL系统库也为应用程序与底层硬件驱动划分了一条清晰的分界线,提高了应用程序的复用性,使得应用程序不受底层硬件变化的影响。

SD卡的上电初始化过程可以分成以下5个步骤:(1)适当延时等待SD就绪;(2)发送74+个spi_clk,且保持spi_cs_n=1spi_mosi=1;(3)发送CMD0

Nios II SPI SD卡 SoPC 嵌入式 相关文章:

- 基于FPGA的8段数码管动态显示IP核设计(02-03)

- 基于Nios II与FPS200的半导体指纹采集系统设计(04-11)

- 基于NiosII的智能多接口片上系统设计(09-18)

- 基于SOPC和DDS IP核的可重构信号源设计与实现(11-03)

- FPGA核心知识详解(3):那些让FPGA初学者纠结的仿真(11-28)

- 基于Nios软核的嵌入式Internet系统设计(07-23)