基于VHDL和CPLD的智能数字电压表设计

时间:10-09

来源:本站整理

点击:

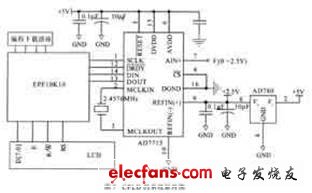

述,进行综合仿真后连接起来的系统电路原理图如图7所位显示在LCD上。

本系统采用的CPLD芯片为ALTERA公司的EPF10K10LC84-4芯片,逻辑门数为10000门,用MAX+PLUSⅡ10.0软件工具开发。设计输入完成后,进行整体的编译和逻辑仿真,然后进行转换、延时仿真生成配置文件,最后下载至CPLD器件,完成结构功能配置,实现其硬件功能。

5 总结

本系统是用CPLD实现的智能数字电压表。随着EDA技术的广泛应用,CPLD已成为现代数字系统设计的主要手段,CPLD目前正朝着更高速、更高集成度、更强功能和更灵活的方向发展。

- 测量仪表基础(二):MC14433组成数字电压表原理与应用(03-01)

- AT89S51实现LED显示数字电压表设计(07-05)

- 基于单片机的LED显示数字电压表(02-08)

- 基于YL-236单片机实训装置的数字电压表的设计方案(02-12)

- 一种简易数字电压表的设计与制作(02-19)

- 数字电压表简易检修程序方案(03-25)