基于CPLD的机载雷达控保系统设计与实现

周期t1进行计数,为低时对周期t2进行计数,电平每发生一次翻转,锁存周期数据data2转入下一个周期计数。采用图4(a)脉冲波形上升沿作适当延时后的波形,用于数字比较器比较的触发条件,当8倍的data1 大于data2时,即发生过d故障。当过d/τ故障连续出现一定次数后,确认为故障,输出相应故障信号。过d/τ保护逻辑框图如图5所示。图6给出了过d /τ保护实时仿真所得的仿真结果。

4.4 i/o接口的抗干扰处理

真空电子管发射机由于具有高压、大功率的特点,对于低压控保电路而言,具备较高的抗干扰能力十分重要。isplsi1032-60lg型cpld本身的抗干扰能力较好,由于cpld的最大工作频率为60mhz,外部微小干扰信号对于cpld来讲,如不对i/o接口信号作数字滤波处理,cpld将认为这是有效信号参与逻辑判断,实际上,对发射机的控制是不利的,会引发故障虚警,若错误地处理故障虚警信息,关闭发射机,则有可能使得本次试验失败,造成损失,以往应用小规模的集成电路的控保就存在类似的问题,并且很难解决。

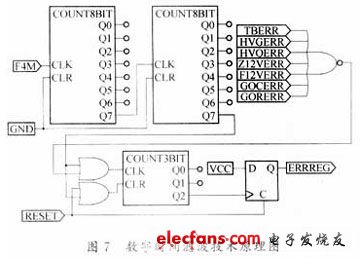

应用cpld技术,解决抗干扰问题应相对容易,图7给出了实际应用中的数字滤波技术原理图,由4mhz信号进行分频计数产生周期为0.25μs ×256×256≈16.4ms的时钟信号,若故障连续出现超过8个脉冲,则认为是真实故障,而干扰信号不会造成故障信号输出。

处理控制信号采用同样的原理,当确认控制信息有效时,进行相关操作。

5 结束语

经试验测试,上述控制与保护硬件电路和软件的设计,具有较好的实时控制能力,在复杂的保护逻辑面前表现出了优越性。基于cpld的控保系统具有性能稳定、抗干扰能力强、体积小、结构紧凑的特点,有较高的推广应用价值。

- 基于可编程逻辑器件的数字电路设计(10-16)

- 基于Xilinx(赛灵思) CPLD的看门狗电路设计(10-09)

- 莱迪思技术专家分享:基于FPGA的视频监控时代(02-21)

- 在测控系统中用IP核实现D/A转换(05-20)

- 基于32位低端嵌入式系统的图像采集模块(04-29)

- 新手福音:概述学习FPGA的一些常见误区(08-27)