基于FPGA的OFDM系统设计与实现

试与性能分析

采用OFDM技术的无线城域网通信系统是一个比较复杂的系统。利用Matlab仿真完成系统可行性论证后,需要考虑如何利用FPGA完成这个算法流程,这需要考虑采用特定FPGA进行运算时有限字长以及浮点运算的特点和系统所占用的FPGA资源,以保证系统的规模不至于过大而超过特定FPGA计算的存储能力。经过在硬件设备上的调试,最终完成采用OFDM技术的城域网无线通信系统。

通过仿真完成可行性论证后,在以Altera公司的EP1C6Q240C8芯片为基础的FPGA硬件平台上,实现了以QPSK为调制形式,以FFT/IFFT变换为主的OFDM技术的城域网无线通信系统。

4.1 IFFT模块

发送端系统的主时钟频率设计为80MHz,整体采用同步时序逻辑。发送端M序列的产生速率设定为80Mbps。送往D/A的数据速率设定为500kHz。在数据接收模块,数据收到后立刻存储,占用时间即为PC发送数据的时间。在QPSK、添零、导频插入模块,由于没有中间存储器,从RAM读出数据,经过映射后就直接输出,整个模块需要256个时钟周期。IFFT 模块采用流水线结构的算法,计算256点 IFFT需要128×8个蝶型单元,合计需要40 960个时钟,加上输入输出所占用的时间,总共约需要41 216个时钟周期(中间有一些状态的跳转,合计512μs)。在数据输出模块,其输入是 IFFT 模块的输出,它的输出速率由 D/A控制。在FPGA中,OFDM调制器的逻辑单元的使用情况见表1,OFDM解调器的逻辑单元的使用情况见表2, IFFT的运算结果见图5。

在表1和表2中,调制器和解调器中所含有的引脚数过多,主要原因是在这些引脚中还含有很多用于调试和测量的引脚,在整个系统调试时,可以将调试和测量用的引脚去掉,只留有数据、地址和控制引脚。

在解调器中需要用到大量的存储单元,但考虑到Cyclone系列的存储单元有限,而逻辑单元丰富的情况,故在解调器中,在几乎耗尽EAB单元时,用逻辑单元来构造所需的存储器,可以实现正常的存储功能。[next]

在开发工程中,主要用到的开发工具由 Altera 公司的QuartusII 及Mathworks 公司的 Matlab。

验证过程如下:

·Matlab随机生成一组128个复数,然后按照 OFDM 帧格式插入0得到256复数点的一个符号,并写入文件(如 datain.dat);

在QuartusII中生成 IFFT 的仿真波形文件(ifft.vwf),另存为 ifft.tbl,并删除其余信号,仅保留 I&Q(输入数据,24bit);

在UltraEdit中打开ifftt.tbl、datain.dat,用datain.dat 中的随机数代替ifft.tbl 中的 I&Q 数据,保存ifft.tbl;

在QuartusII中打开 ifft.tbl,将I&Q复制到 ifft.vwf 中,开始运行仿真;

·将仿真结果另存为dataout.tbl,用Matlab读取与原数据在Matlab下的IFFT变换结果进行比较分析。

给出一组随机数据输入,经过FPGA中的IFFT模块变换得到时域幅度如图6(实部)、图7(虚部)所示。

而将同样的随机数经过MATLAB变换,得到的时域幅度如图8(实部)、图9(虚部)所示。

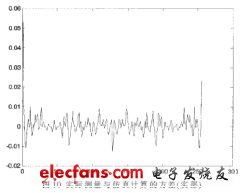

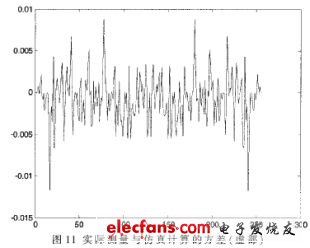

实际测量与仿真计算的方差分析如图10(实部)、图11(虚部)所示。两者结果基本一致。

4.2 帧到达检测同步模块

对于帧到达检测同步系统,要求尽可能在较短的时间内建立同步,并且在帧同步建立后应有较强的抗干扰能力。通常用漏同步概率P1、假同步概率P2和同步平均建立时间ts三个性能指标来表示同步性能的优劣。在本文的帧同步信号提取电路的建模与设计中,是以7位巴克码识别器作为帧同步码组的。在同步系统处于捕获阶段时,设置自动判决门限为7;在帧同步建立以后,则把判决门限降为6,这样做的目的一方面是减少假同步的概率,另一方面是为了减少漏同步的概率。

漏同步概率P1:

假设系统的误码率为P,7位码全部正确的概率是(1-P)7,因此判决门限电平为7时的漏同步概率为P1=1-(1-P)7。若将判决门限改为6,此时允许有一位错码,出现一位错码的概率为C71P1(1-P)6。漏同步概率为P1=1-[(1-P)7+C71P1(1-P)6]。一般地,设帧同步码组数目为n,判决器容帧同步码组中最大的错码数为m,则漏同步概率为:

从前面的帧同步系统的设计可以了解到,识别器只能被动地识别与帧同步码组相同的码组,如果在信息码组中也出现了与帧同步码组相同的码组,这时识别器会把它误认为帧同步码组而出现假同步。

比较式(1)和式(2)可以看出,当m增大时,P1减小,P2增大,两者是矛盾的,另外还可以看出,当n增大时,P1增大,而P2减小,两者也是矛盾的。因此m和n的选择要兼顾P1和P2的要求。

平均同步建立时间

- OFDM技术在应急通信系统中的应用(08-28)

- OFDM技术简介(10-11)

- OFDM应用中的关键技术解析(10-11)

- OFDM系统仿真与分析(10-11)

- 基于DSP的OFDM系统设计(10-11)

- 基于PLC和OFDM技术的电力线载波技术在工厂数据传输中的应用(03-02)