基于CPLD和ISA总线的数据采集系统设计

。

从图4中可得到ADS7816在片选信号下降沿到来后的14.5~15个时钟周期里,完成一次转换并逐位输出12位转换结果。为了能够得到完整的正确的A/D转换结果,采用计数方式设置标志位FLG。在ADS7816的片选信号为低电平的前15个时钟周期中,即"计数器计数值≤14"时,FLG=l,表示A/D转换正在进行;当"计数器的计数值》14",则FLG=0,表示A/D转换结束。当FLG=0时,程序可读取一次正确的A/D转换数据。

因为ADS7816的数据转换结果是串行输入到CPLD中,需在CPLD中将得到的数据进行串并转换后再通过ISA总线的8位数据线分2次送出。

系统进行数据转换前需先选择输入通道,确定采集哪一路信号。上位机输入的通道号经CPLD送至8路模拟采样开关。

2.2 数据采集测试程序设计

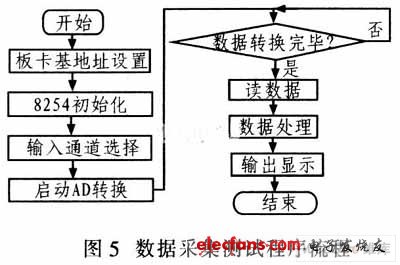

上位机的数据采集测试程序采用C语言设计。因为系统采用ISA接口,所以功能测试无需编写复杂的应用程序,只需在Win98操作系统里编写C语言的测试程序即可实现系统的数据采集功能。上位机的数据采集测试程序主要完成:采集系统的硬件初始化、通道选择、数据采集、数据处理和数据输出。其程序设计流程如图5所示。

3 仿真和实验结果

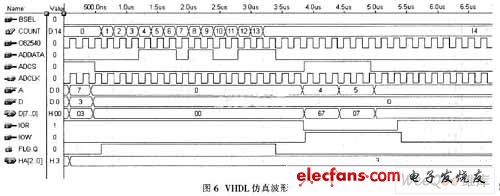

图6所示为写入XC9572的VHDL程序的仿真波形,主要是CPLD控制A/D转换的功能仿真。从仿真波形图中可以看出,当地址A为7时,写入通道号3,得到的输入通道选通信号为3,实现通过上位机选择输入通道功能。当ADCS的下降沿到来后开始启动A/D转换;ADCS下降沿起的第3个时钟对应的ADDATA为系统转换的第1个数据,直到这次转换完毕。由给定的ADDATA数据得知,串行输入的数据是767H(011l O110 0111B)。仿真结果中,地址为4时,数据的低8位结果为67H;地址为5时,数据的高8位结果为07H,仿真结果完全正确。

在Windows98下,使用基于C语言的数据采集测试程序,可得到如表l所示的测试数据。从所列数据看出,该数据采集系统采集数据正确,且精度高。

4 结论

基于CPLD的数据采集系统具有硬件线路简单、精度高、采集速度快的特点。ISA总线和CPLD结合的数据采集系统有其独特的优势。该数据采集系统可循环采样多路(8路)模拟信号采样。实际测试结果表明该设计方案可行,且具有很高的实用价值。

- 基于DELPHI的镍氢电池管理系统软件设计(12-20)

- 基于ISA总线的高速同步数据采集系统设计(05-06)

- 基于计算机的测量仪器的内部和外部校准(10-08)

- 基于AD73360和TMS320F2812的数据采集系统设计(12-06)

- 基于暂态行波法的配电网故障定位装置研究(02-01)

- 数据采集处理系统在电力中的应用设计(12-30)