ECL PECL LVPECL信号都是什么?它们的优缺点和电路图详细剖析

时间:03-26

来源:网络整理

点击:

VIH窗口之内,Driver的VOL范围全部落入Receiver的VIL窗口之内时,可以保证Receiver可以正确接收Driver的输出,否则会有潜在的互连不正确甚至损坏器件的可能。

2、差分信号

对于差分信号,要关注的指标是输入共模电平VCM和差分信号VDIFF范围。

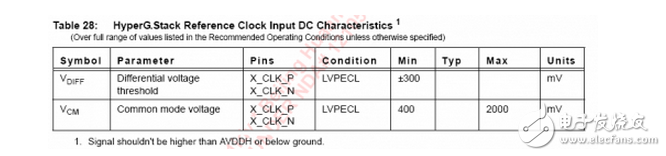

如某器件的某输入口工作在LVPECL模式下。其指标如下(AVDDH=2.5V):

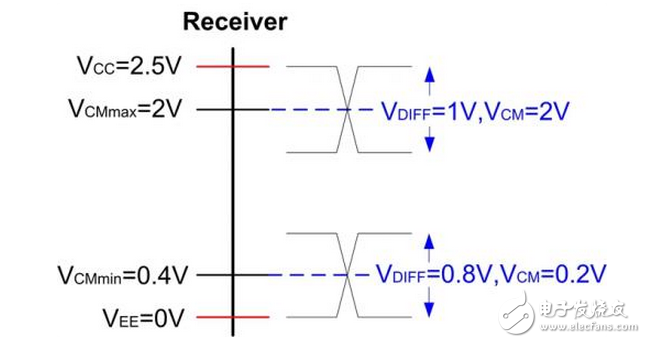

那么其接收窗口如下图所示,图中标出了共模电压为最大或者最小时,其允许的最大单端电压。

只要落在这个范围内的差分信号,即同时满足:

1.输出|VDIFF|大于300mV;

2.输出共模信号VBB位于400 mV到2000mV之间;

3.输出的单端信号不能超过VCC或者VEE;

满足以上条件的差分信号都可以被正确接收。可以注意到,如果共模信号被端接到VBB =VCC-1.3V,接受窗口最大。

由上可见,差分信号有比单端信号宽得多的接收窗口,这也是高速应用中差分信号被普遍采用的原因之一。

- I/O接口标准解析系列教程(2):CML、PECL、LVECL和LVDS(02-07)

- LT3751如何使高压电容器充电变得简单(08-12)

- 三路输出LED驱动器可驱动共阳极LED串(08-17)

- 浪涌抑制器IC简化了危险环境中电子设备的本质安全势垒设计(08-19)

- 严酷的汽车环境要求高性能电源转换(08-17)