基于FPGA的OLED真彩色显示设计方案

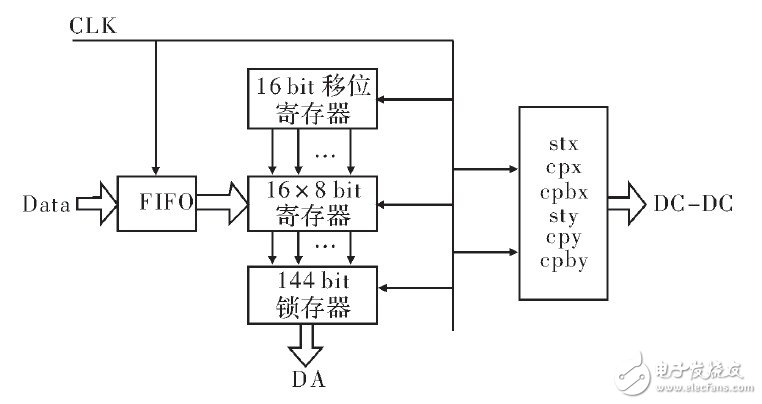

,它的输出端接16 个8位数据装载寄存器的片选端,这样16 个8 位数据装载寄存器逐个被选通,此时这些数据就可以载入到16 个8 位数据装载寄存器中,这16 个8 位寄存器的输出端接在144 位锁存器的输入端上。16 个时钟clk_reg 上升沿过后, 16 个8 位数据装载寄存器都将依次被装载满,此时数据锁存信号Lock 到达,将144 个数据锁存到144 位数据锁存器中,然后这些数据进入到DA 转换模块,转换成16 路模拟量,送至OLED 显示屏,完成一个Block 数据的载入。

在列扫描驱动脉冲cpy 和cpby 的控制下,80 个Block 依次被选通,在每一Block 被选通期间,都将进行一次144 个数据的移位寄存和锁存,当80 个Block都锁存完之后,一行数据的载入也就完成了。当第一行的80 个Block 数据显示完毕后,列扫描起始信号sty过来,又开始从第一列扫描,与此同时,在行扫描驱动脉冲cpx 和cpbx 的作用下,第二行像素被选通,所以,这时将进行第二行的1 到80 个Block 的数据载入,以此类推,直到90 行数据都显示完毕之后,行扫描起始信号stx 到来,重新选通第一行,循环往复,一帧帧地显示数据。

2 仿真结果

选用Altera 公司Cyclone Ⅲ 系列芯片EP3C10E144C8 为目标芯片,采用Verilog HDL 语言进行设计,在GX - SOPC - EDA - EP3C10 - STARTER -EDK 开发板上进行Modelsim 仿真,仿真结果如图4 和图5 所示。

图4 外围驱动时序仿真结果

图5 256灰度产生模拟仿真

由图4 仿真结果可以看出,80 组列扫描脉冲cpy和cpby 控制80 个Block, 80 个列扫描脉冲完毕后,列扫描起始信号sty 脉冲开始,继续扫描下一行。90 行扫描完毕后, stx 到来重新选通第一行,依此循环,符合设计的要求。

由图5 仿真结果可以看出,对于输入的8 bit 像素数据,经灰度产生模块转化为灰度数据。以第一个输入数据8 hff 为例,每位的显示时间为128∶ 64∶ 32∶ 16∶ 8∶ 4∶2∶ 1,由其不同组合,从而实现了256 级灰度的功能。

3 结束语

基于FPGA 芯片设计了分辨率为480 × RGB × 640的真彩色OLED 显示屏的驱动电路,在传统的子场原理和脉宽调制占空比实现灰度的基础上,对其进行优化,采用R、G、B 单基色像素分时显示的方法,实现了256 级灰度功能。经仿真和软硬件协同仿真验证,实现了设计所要求满足的功能。其256 级灰度实现方法简单灵活,降低了对FPGA 驱动频率的要求,对于在高刷率、高分辨率、高灰阶显示器件上的应用,具有很高的实用价值。利用该电路系统可以实现OLED 显示的全彩色实时动态图像的传输,为今后OLED 作为大尺寸显示器提供了技术支持。

- OLED显示器结构/特点/原理(12-15)

- OLED在头戴显示器领域的应用(11-11)

- 友达光电明年将主攻OLED液晶面板(10-12)

- 应用在便携设备视频播放的高速OLED驱动芯片(03-01)

- 曲面OLED电视的优点与挑战(07-22)

- 细数OLED显示技术的“十宗最”(08-04)