基于FPGA技术实现对嵌入式系统的在线监控

在SoC系统的设计及使用过程中,对其内部行为的实时监控十分重要,目前普遍通过监控端和目标系统间的监控信息通信来实现,UART常用作通信信道。

目标SoC系统常使用中断方式或轮询方式获取监控通信数据包,对其解析并进行相应数据操作后回复应答信息。中断方式中SoC需完成保存中断现场、调用中断服务程序、恢复现场系列任务,上下文的切换占据了系统额外开销;轮询方式中,系统定时检查设备请求,若有数据到达则调用相应处理程序,固定的轮询周期增加了数据等待处理时间,数据量较小时频繁查询造成对CPU资源的浪费。

针对上述问题,提出一种的新监控方法,设计一个FPGA通信系统,由其作为SoC与监控计算机数据交互的桥梁,负责完成在线监控的通信过程,保证被调试系统和调试主机之间调试信息和命令的交互可靠性,可避免目标SoC频繁的处理通信中断,提高其控制性能。监控功能实现机制与通信系统主要模块的设计方法将被讨论,通过对比嵌入式CPU在不同监控方法中的通信时间消耗,说明该方法具有一定实用价值。

1 系统组成结构

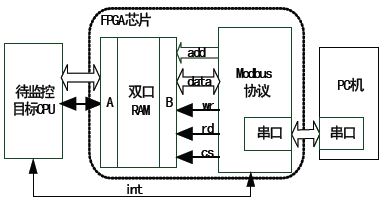

基于FPGA设计片上通信系统如图1所示,其主要组成部分为Modbus解析模块和双口RAM存储模块。上位机发出监控命令帧数据时,由Modbus模块完成命令帧的接收、解析过程,并将待操作地址、数据等信息存入双口RAM中,目标CPU据此将自身内存映像区的相应数据一次搬入双口RAM,搬移完毕后,Modbus协议模块进行应答数据组帧,并向监控上位机发回应答数据,实现对监控数据的实时可靠采集。

图 1 通信系统组成结构

2 基于双口RAM的数据交互设计

2.1 双口RAM定制及内存映射设计

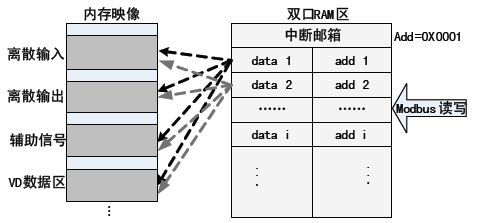

目标SoC中的待监控数据状态量在内存中的存储方式,可抽象表示为如图2中内存映像。

图 2 双口 RAM 的内存映射机制

双口RAM中存储当前待监控数据对象集合,是目标CPU内存映像区的一个数据子集。由于当前监控对象可随机落在内存映像区的任意存储块上,双口RAM的内存映射方式选取为随机映射,如图2所示。

分散存放于CPU内存映像区的监控对象,映射为双口RAM中的连续存储区。上位机基于Modbus协议与FPGA片上系统通信时,访问连续的地址单元,保证了数据访问速度,提高系统的通信效率。

2.2 双口RAM中的数据操作设计

2.2.1 上位机对双口RAM的读写操作

PC上位机为通信发起方,通过串口与FPGA片上系统连接,采用Modbus-RTU协议进行数据通信,完成对运行参数的读取和写入等操作,实现监控功能。

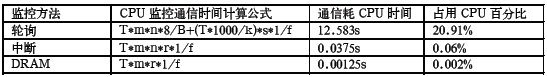

表 1 监控通信过程占用 CPU 时间

用户在人机界面输入本次待监控对象信息, 后台软件依据Modbus帧结构及约定的双口RAM内存映射机制,组成监控命令帧并通过串口发出。FPGA片上系统对收到的命令帧进行解析,获取操作功能码、目标地址、数据包大小等信息,据此向双口RAM区写入待操作数据地址集,写入完毕后向目标CPU申请通信中断。根据Modbus命令帧中给出的数据操作长度,一次可对多个数据单元进行读/写操作。

2.2.2 目标CPU对双口RAM的读写操作

目标CPU收到通信中断请求后,读双口RAM区的中断邮箱,邮箱信息包含本次申请功能(读或写)及申请的数据项个数等。根据申请地址集,将自身内存映像区相应数据集一次搬入双口RAM,或将双口RAM中数据集一次搬入内存映像区相应地址处,搬移完毕后,清空中断邮箱,向监控模块发出中断应答。

3 Modbus协议栈模块的设计与实现

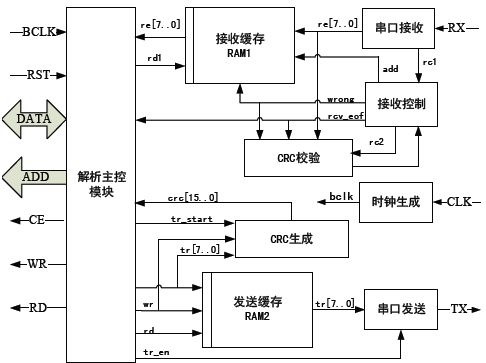

采用自顶向下的设计方法,根据功能需求设计Modbus协议栈顶层原理框图如图3。使用VHDL硬件描述语言编程实现各组成子模块,功能如下述。

图 3 Modbus 协议栈顶层框图

(1)时钟生成模块:通过分频和相移产生位时钟clk和1/16位时钟bclk,作为控制其他模块的运行节拍,保证系统运行同步。

(2)串口接收模块:以bclk作为控制时钟,对接收的位数据作中点采样,进行串并装换得到字节数据。

(3)串口发送模块:以bclk作为控制时钟,发送使能信号有效时,输入端的字节数据进行并串装换,通过串口发出。

(4)接收控制模块:判断帧的起始、结束、是否接收错误;提供地址数据,接收的字节数据被存储至RAM1中相应存储单元。

(5)CRC校验/生成模块:使用基于字节的CRC_16校验码运算方法。接收端的校验过程与数据接收同步进行,接收控制模块每收到一个字节数据,CRC校验模块对其作一次CRC码计算;CRC生成模块运行机制类同。同步运算可有效减少一次对帧数据的遍历。

(6) 解析主控模块:作为系统的核心,负责解析收到的命令帧,根据解析信息进行数据读写操作,组成应答帧

- 2DPSK低频感应通信系统MATLAB仿真(10-18)

- 基于FPGA的通信系统同步提取的仿真与实现(03-11)

- 基于触摸屏和DSP的串行通信系统设计(10-13)

- 无线通信信号干扰分析与解决攻略(08-05)

- DE0-Nano-SoC 套件 / Atlas-SoC 套件(10-30)

- 高压电池组监视器可实现先进的电池系统(10-14)