汽车显示器接口设计关键技术分析

IMS Research的调查显示,带有视频功能的汽车音响主机的数量将会由2006年的850万台增长到2015年的2660万台。为了既能向驾驶员提供信息,又不分散其注意力,显示器需要安装在远离汽车音响主机的位置,并将画面投影到挡风玻璃的背面。这种结合了图像源和面板的视频接口正在越来越多地从模拟视频技术转向质量更高的RGB(红绿蓝)数字视频格式,后者已成为LCD显示器中使用的标准接口。前端显示应用的电缆长度通常保持在1到3米的范围内,而后座娱乐(RSE)单元的电缆则需要达到8米甚至更长。这种连接支持千兆位/秒的数据传输速率,远超过传统车载网络的波特率,并可以利用点对点串行器/解串器(SerDes)解决方案完美实现。与传输一路较宽的并行视频总线相比,这种芯片组大大降低了传输线和连接器的引脚数量,从而实现了出众的系统级优势。

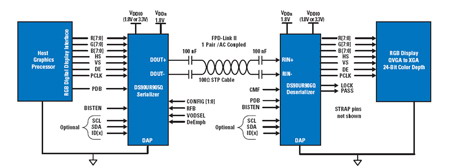

为满足汽车显示器接口方面的严苛要求,比如高数据吞吐量、超薄布线、高级信号调节、可检测性以及超低EMI(电磁干扰)等。美国国家半导体(NS)公司开发出DS90UR905/6 和DS90UR907/8 SerDes芯片组,该产品是能将分辨率从QVGA(400 x 240)扩展到24位色深的XGA(1024 x 768)的嵌入式时钟SerDes解决方案。宽范围的像素时钟频率使汽车制造商只需在其整个车型系列中采用一个数字视频显示接口方案,即可覆盖从双画面的小仪表盘面板、中控台的LCD到更大尺寸的RSE显示器应用。

视频应用和SerDes概念

SerDes组件的目标应用领域是平板显示器链路接口,它可以通过一根较长的串行电缆把图像主机与显示器连接起来。典型的例子包括:中央信息显示器(CID)、仪表盘、头枕上的娱乐显示器或为后座乘客准备的车顶下降式显示模块,如图1所示。这些新型芯片组是NS推出的"FPD-Link II"系列产品中的一组,它们可以将一个视频源的27位数字RGB色彩信息和时间控制信号转换成一个嵌入了时钟信息的单一串行数据流在双绞线上传输。芯片组在I/O(输入/输出)层采用高速的差分信号,也就是说,在"真"(正)端子上传输实际信号的同时,"互补"(负)端子上传输与之对应的相反极性信号。

图2在系统层面上描述了视频传输的概念。除了颜色和时序位外,还有一个可选的I2C控制接口,它可替代通过常规引脚带选项实现的组件配置。芯片组支持18bpp(每像素位)或24bpp的色深。彩色显示器使用3个子像素(红、绿、蓝)来定义一个单独的像素。由于每个像素有18位(6位红,6位绿和6位蓝),我们可以得到26.2万种颜色。大多数人的眼睛可以看到1000万种以上的颜色,这也就解释了为什么使用24bpp已成为趋势:它能提供超过1600万种颜色,可实现更丰富的用户体验和平滑的颜色梯度。像素时钟范围现已极宽:频率可从5MHz 到65MHz,这使得串行链路速率从140Mbps提高到1.82Gbps,涵盖了汽车显示器的全部主流分辨率。

并行LVCMOS输入和输出信号可以分别灵活地对准同步发射器输入及接收器恢复输出时钟(PCLK)的上升沿或下降沿,这一特性大大简化了串行器至图像控制器以及解串器至LCD计时控制器的接口连接。在发射器并行时钟周围的一定频段内,SerDes芯片组在"预同步"接收器的PLL时无需外部参考时钟(石英或振荡器)。甚至在一切可能的随机数据模式传输过程中该同步都能得到保证,这被称为"随机数据锁定"特性。这不仅节省了参考组件系统的成本,而且消除了另一个潜在的电磁干扰源。该性能还可以实现"热插拔",即在不需要任何特殊排序或训练模式的情况下,就可以对送往解串器的串行数据流执行断言/取消断言操作。

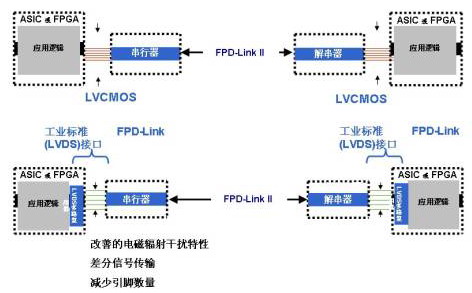

一旦接收器PLL锁定在发射器的频率下,即可由LOCK输出标志引脚显示这一状态,确保接收器输出的数据完整性。DS90UR907/8芯片组具有DS90UR905/6芯片组的一切特性,两耳区别在于输入输出不再是发送LVCMOS信号的并行总线,而是遵照开放的工业标准"FPD-Link"。很多现代化的图像控制器、显示定时控制器、ASIC和FPGA都支持这种"一级串行化"技术,它采用适合18bpp的3个数据通道,或者适合24bpp的4个数据通道,每一个都有一路并行时钟通道。电信号的发送遵循开放的ANSI/TIA/EIA-644A标准,该标准又称作"LVDS"(低压差分信号传输)。使用该接口技术代替常规LVCMOS的优势在于:采用差分信号可降低电磁干扰,并减少组件的引脚数量,如图3所示。

图3 FPD-Link系统接口选项的优势

FPD-Link II有效负载

在每一个像素时钟周期内,28个"次符号"在差分I/O上经过时分多路复用,转换成一个串行数据流。嵌入的有效负载包含24个颜色位、3个定时信号(水平同步-HS、垂直同步-VS和数据使能-DE)以及附加位。互连线路速率为28x像

- 严酷的汽车环境要求高性能电源转换(08-17)

- 电源监视器LTC4151对汽车应用的解决方案(08-10)

- 用节省燃料的启动/停止系统为汽车电子产品供电(08-17)

- 汽车刹车灯及其他LED信号灯的准确“暗淡”/“明亮”控制(08-12)

- 适合有源天线系统并内置保护和诊断功能的坚固、低噪声、稳定型电源(08-16)

- 新的汽车显示屏需要能提供30,000:1调光比的背光照明LED驱动器(08-23)