基于FPGA技术的全方位移动机器人运动控制系统的方案设计

0 引言

目前,全方位移动机器人由于具有出色的灵活性,已经成为RoboCup中型组足球机器人比赛中最理想的选择。而机器人的运动控制一直以来都是直接影响机器人性能的主要因素,也是移动机器人研究的热点之一。本文研究了一种用FPGA技术实现三轮全方位移动机器人运动控制系统的方法,与双DSP结构,DSP+CPLD结构,以及DSP+专用集成电路结构等相比,该方法具有简单可靠,扩展性强等特点。且FPGA设计简单,使用方便,开发周期短,能够实现真正的SOPC系统。

1 全方位移动机器人运动模型

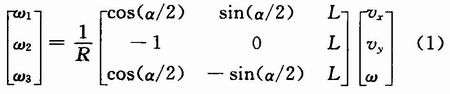

设世界坐标系下机器人的速度为ε=[vx,vy,φ],则当vx=O,vy≠0,φ=O时,机器人做前后方向的直线运动,当vx≠0,vy=0,φ=0时,机器人做左右方向的直线运动,当vx=0,vy=0,φ≠0时,机器人做自转运动。图1中,ω1,ω2,ω3为3个主动轮的转动角速度,R为全向轮半径;L1,L2,L3为机器人车体中心到3组全向轮中心的水平距离,设有L1=L2=L3=L。α为前两轮之间的夹角,另外2个夹角均为180°-α/2。则机器人坐标系下的速度到三轮速度之间的关系如下:

由式(1)可以看到:知道了机器人在平面世界坐标系中的速度要求后,便可以得到主动轮的速度要求,进而对电机发出相应的控制信号。

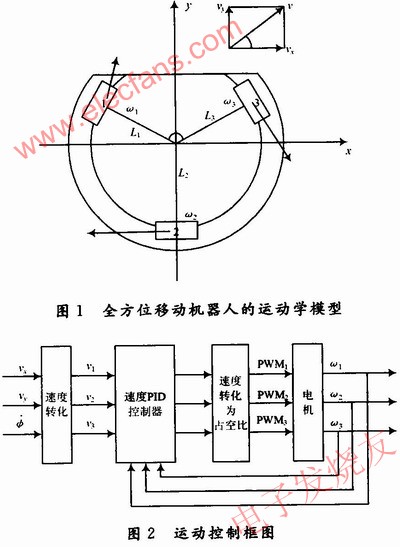

2运动控制方案本系统总体设计思路如图2所示,首先通过RS 232接口,实现PC机与底层控制芯片FPGA的通信,FPGA在接收到相关的机器人坐标系下的速度后,将机器人坐标系下的速度值转化成机器人3个全向轮子的角速度,将得到的角速度值计算出相应的占空比,生成相应占空比的PWM波形,输出信号接到直流伺服电机驱动器,然后通过FPGA采集正交编码盘信号,计算出轮子实际的角速度值,做PID速度闭环控制。鉴于FPGA模块复制的优势,这里对每个全向轮分别做了PID闭环控制。

3 系统硬件设计

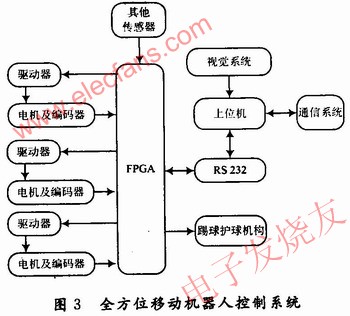

采用的三轮全方位移动机器人系统框图如图3所示,上位机主要完成图像信息的采集、处理、路径规划,并实现与场外裁判盒的通信。下位机主要是FPGA,主要实现三轮编码信号的采集,PID速度闭环控制,踢球控制,电机控制信号的产生,还有其他的传感器信息的采集等,并负责与上位机之间的信息交互。本设计只是完成了下位机运动控制部分。

3.1 正交编码信号采集与测速实现

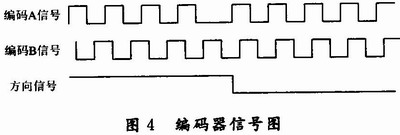

增量式光电编码器输出信号如图4所示。

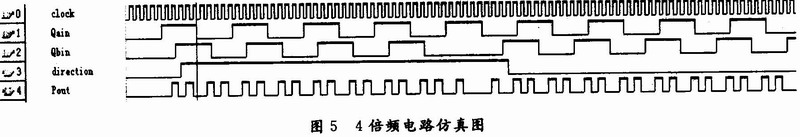

A、B两相信号是相位相差90°的正交方波脉冲串,每个脉冲代表被测对象旋转了一定的角度,A、B之间的相位关系则反映了被测对象的旋转方向。在FPGA中设计4倍频和鉴向电路,本设计采用2路输出:一路输出方向,另一路输出脉冲,并对鉴向倍频电路进行仿真,如图5所示。

根据脉冲计数来测量转速的方法有M法、T法以及M/T法3种。M法适用于高速测量场合,在低速时有较大的误差;而T法,恰恰相反,在低速时测量准确,高速时误差较大。

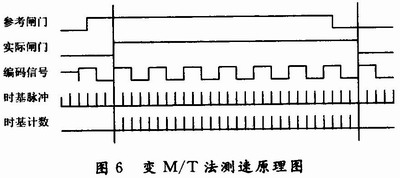

本设计采用文献所描述的方法。该方法如图6所示,设定参考闸门时间为固定的1个值,它只是作为参考信号和编码信号共同确定实际的闸门时间。这样确定的闸门时间为被测信号的整周期倍,能够有效提高测量精度。则测得的速度为:

4. 增量式PID控制原理及其FPGA实现

实际机器人的数学模型不可避免地存在一定程度的参数不确定性,且三轮全方位移动机器人的正交全向轮在行走时会与地面交替接触而产生一些不确定摩擦转矩,这些都会给机器人的精确控制带来难度。为了对三轮全方位移动机器人进行精确的控制,系统采用PID速度闭环控制算法对机器人的3个全向轮进行速度调节。

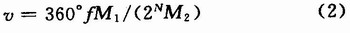

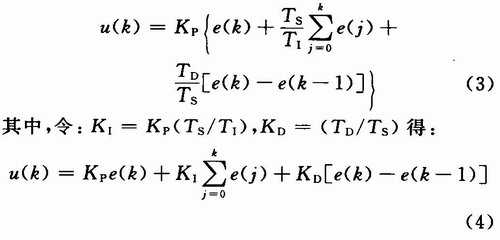

令采样周期为TS,将连续PID公式离散化后可得到数字PID算法表达式:

式中:k为采样序号;u(k)为第k个采样时刻的计算机输出值;e(k)为第k个采样时刻的计算机输入误差值;e(k-1)为第k-1个采样时刻的输入误差值;Kp为比例系数;KI为积分系数;KD为微分系数。

这种算法虽然比较直观,但由于是全量输出,所以每次输出均与过去的所有状态有关,计算时要对e(k)进行累加,计算机运算量大。

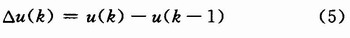

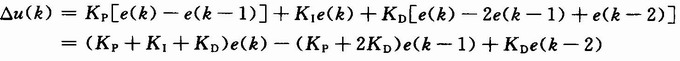

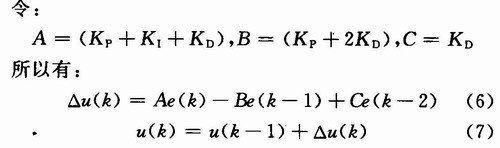

于是产生了增量式PID算法:

上述公式(7)为增量式PID控制算法。只输出控制增量,误动作影响较小,且控制增量只与最近几次的采样值有关,容易通过加权处理获得比较好的控制效果。

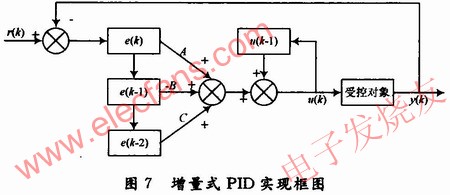

根据以上公式推导,结合FPGA的工作特点,本文设计了适合FPGA的增量式PID实现结构。

由图7可以看出,增量式PID控制算法程序结构,只要最近的3个误差采样值就可以加权计算。这在FPGA内部完全可以并行实现,移位部分结构类似FIR滤波器的实现结构,难点是FPGA设计时对有符号数的熟练操作和保证累加器不能溢出。

一种高效的硬件测试手段和系统测试方法,它能

- 运算放大器选择指南 助您获得上佳的噪声性能(09-10)

- 运算放大器组成阶梯波发生器电路图(10-11)

- 电流互感器运行特性分析(02-22)

- 运算放大器的噪声(04-07)

- 运放电源过压保护电路设计(06-28)

- 保护运放电源电压极性反接措施及其电路设计(06-28)