基于CMOS工艺的数字步进衰减器的设计

|

DSA通过一个友好的处理器接口控制RF信号强度,被广泛应用于多种RF产品,比如宽动态范围接收器、功率放大器的失真信号消除环路,以及各种有线电视分配系统。

DSA通常具有"线性增益"的特性,是ADC与外界之间的普通接口。与模拟的解决方案相比,它们能提供更高的精确度、更好的温度稳定性以及更小的失真,此外还具有尺寸小、功耗低、易于实现等特点,是一种富有成本效益的解决方案。

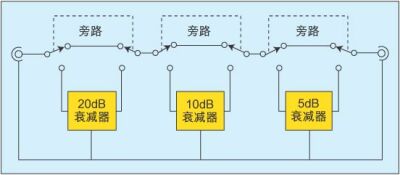

本文的讨论虽然集中于Peregrine半导体公司的PE4302(50Ω)与PE4304(70Ω)这两种6位DSA器件上,但实际上这种DSA通用设计方法适用于所有类似产品。 图1是一个典型的步进衰减器,衰减器的每个管脚位于两个单刀双掷(SPDT)开关之间。机械式继电器或开关能提供几乎无损耗的接触,经过仔细设计,这种结构能提供很低的插入损耗和优良的隔离度。

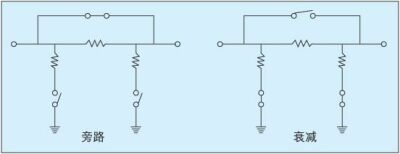

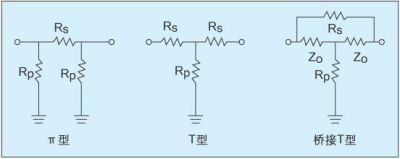

图2是π型衰减器经过改进的单刀串联开关结构。在每个单元都由一个串联SPST和两个旁路SPST代替原来的两个SPDT。实际上,这一技术将每个单元的插入损耗(IL)降低了一半,SPST结构也比SPDT更简洁,同时性能更好,特别是在高频的时候。 由于所有无源衰减器均为三端网络,这种串联/旁路设计需要与其它拓扑结构一起工作,如T型和桥接T型(见图3)。可能是由于所受培训或者习惯上的原因,工程师似乎更倾向采用π型结构,但是在一个电阻值跨度很大的单片电路中,这可能并不是最好的选择。 设计分立电阻时,电阻值不是一个重要问题。然而在集成电路中,具有特定电阻系数的矩形面积决定了电阻的阻值,这种表面电阻在CMOS工艺中通常约为200Ω/square。集成电路设计面临的难题是,不管电阻值是多倍于200Ω还是远小于200Ω,电阻值都已经成为设计及制造过程中的一个棘手问题。

|