基于CMOS工艺的数字步进衰减器的设计

| 图4:UTSi (RON/COFF)技术的发展图。 |

设计阻值非常大或非常小的电阻都需要很大的面积以及很高的成本。大阻值的电阻是长而薄的方形设计,而小阻值的电阻则具有很宽的外形以避免公差问题。表1给出了最低有效位(LSB)为0.5dB的50Ω 6位二进制衰减器的电阻值,其中Rp和Rs分别代表每一个网络中的旁路电阻和串联电阻。

在表1第一行,步进值为0.5dB,这时π型及T型网络所需的电阻比约为600:1(1738/2.9及868/1.4),而桥接T型网络所需的电阻比只有它的一半,约为300:1(844/3)。当步进值为1dB和2dB时,桥接T型网络仍然保持了较低的最大电阻值/最小电阻值的比率,它的电阻值范围缩小了一半,其代价只是增加一个电阻。

|

|

| 图5:典型的插入损耗与温度之间的关系。 |

当步进值等于或大于4dB时,T型网络的Rpp值较高而成为最佳选择。这形成了一个普遍策略:当步进值较小时使用桥接T型网络,当步进值较大时使用π型网络。

无论是哪种情况,要使DSA具有较高的准确度、优良的线性度、最小的工艺误差以及最佳的温度记录,就需要每一个电阻的阻值远远大于相应开关的导通电阻RON。对于较低的dB值,T型结构的Rp值较高,约为几百欧姆,相比之下旁路开关的RON(通常只有几欧姆)显得很小。同样,当dB值较大时,π型网络旁路电阻的阻值也较大,远远大于旁路开关的RON。

优化方法

|

|

| 图6:PE4302的1dB压缩点与频率的关系。 |

低RON和低关断电容COFF对于串联FET开关而言都是必不可少的。RON低意味着插入损耗小,但这也意味着需要使用COFF较大的大器件。但是高频工作环境却要求采用COFF很小的小器件,以便使串联阻抗和隔离度都很大。这种矛盾可通过采用能提供适当隔离度的最大器件来解决。例如,当步进值为1dB时,串联开关的隔离度为20dB就很好了。对于一个步进值为20dB的衰减单元而言,隔离度同样为20dB的串联开关,只有17dB为净变化,其余3dB则为误差。对于这点,有的工程师可能会说:"好吧,那就用更高的衰减值来补偿。"理论上这是可行的,但是在实践中,隔离度并不很具重复性,COFF只要有一点点变化,隔离度就会变化很大,因此必须确保对于每一个步进值都有合适的而非过大的隔离度。

电压额定值是另一个可进行优化的地方。每一个串联开关都必须有一个与其衰减值成比例的最高工作电压,例如,衰减步进值小则入射电压下降幅度也较小。旁路开关则完全不同,试想一下零dB结构中的衰减器,所有衰减器都被旁路,每一个旁路开关都必须能承受满摆幅输入电压。

|

|

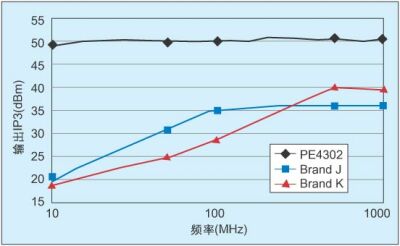

| 图7:IIP3的对比(工作电压为3V,插入损耗为0dB)。 |

无论是串联开关还是旁路开关,任何一个特定开关都是由一个、两个、三个或更多串联FET器件组成。因为多个串联FET可以分担入射电压以达到所需的压缩及截取点,所以预期的电压值决定了FET器件的具体个数。随着串联器件数量的增加,晶