基于DSP的OFDM系统设计

时域。

3.加入循环前缀(数据个数由64个变为80个),防止多径延迟。

4.通过DMA将数据送到Mcbsp发给FPGA。

接收端

5.由Mcbsp接到数据通过DMA存入数据空间(此时数据应该与第四步结束时相同)。

6.去掉循环前缀(数据个数又由80个变为64个,此时数据应该与第三步结束时相同)

7.作64点FFT变换(此时结果应该与第一步结束时相同)

8.去掉插入的数据,反映射(数据个数由64个变为56个,此时结果应该与第一步开始时相同)并解码。

2.3 DSP串口的接发配置和DMA的设置

系统实现关键在FFT的实现和DSP串口的接发配置和DMA的设置。这里详细说明串口和DMA的设计方法。

系统用Mcbsp1发送数据,用Mcbsp2来接收数据,为了不占用过多的CPU资源,用DMA的4通道来传送数据给串口,用5通道来接收数据。对于DMA和Mcbsp的使用主要是寄存器的配置问题,在这些配置当中可以对工作模式等一系列东西进行设置。现分别介绍如下:

对于Mcbsp来说,接收和发送可以配置在一起,采用了DSP自身带有的CSL库函数,它对寄存器的配置是通过结构体来定义的,可以方便的修改成自己所需要的模式。

在进行将DSP片内数据地址赋DMA中的地址时要注意,DMA中数据是以byte为单位存储的,存储的最小数据单位上byte,而片内存储区间是以word为单位的,所以将地址交过去时,要将地址右依、移1位。如:

srcAddrHi = (Uint16)(((Uint32)(dmaXmtConfig.dmacssal)) >> 15) & 0xFFFFu;

srcAddrLo = (Uint16)(((Uint32)(dmaXmtConfig.dmacssal)) << 1) & 0xFFFFu;

dstAddrHi = (Uint16)(((Uint32)(dmaXmtConfig.dmacdsal)) >> 15) &0xFFFFu;

dstAddrLo = (Uint16)(((Uint32)(dmaXmtConfig.dmacdsal)) << 1) & 0xFFFFu;

在进行中断处理是时,要注意执行的顺序,首先要保存原来的中断向量表,再清除原来的中断,然后将局部中断允许位开放(即关屏蔽位),开全局中断,最后将中断服务程序填入中断向量表。

old_intm = IRQ_globalDisable();

IRQ_clear(xmtEvenTId);

IRQ_enable(xmtEvenTId);

IRQ_setVecs(0x10000);

IRQ_plug(xmtEvenTId,&dmaXmTIsr);

在程序任务完成之后,还要记得还原中断,关掉Mcbsp和DMA。

MCBSP_close(hMcbspr);

DMA_close(hDmaRcv);

DMA_close(hDmaXmt);

DMA_stop(hDmaXmt);

IRQ_disable(xmtEventId);

DMA_stop(hDmaRcv);

IRQ_disable(rcvEventId);

在设定的控制字下,串口1将以CPU时钟频率的1/70发出帧定位信号,宽度为一个码元长度,上升沿有效,以帧定位信号的1/80发出时钟定位信号(因为一帧有80个元素),也是上升沿有效,发送元素是32bit的数,这是因为发散的数据是复数,分为虚部和实部,先放实部后放虚部,所以一个元素是32个bit。

串口2是接收端,接收外部帧同步信号和时钟同步信号用来同步。外部传来的各种信号和数据格式和串口1发送的相同,不过收的时钟定位信号是下降沿有效。

在DMA方面,通道4是发送通道,通道5是接收通道,同步事件分别是发送串口和接收串口,在一个数据串口接收到了后会发中断给DMA,使其接收数据或传下一个数据,所以在发端,需要手工先送一个数据过去。

3 性能分析

可靠性以外,速度是一个通信系统最重要的评估因素,而数据的处理速度在很大程度上限制了传输速度,成为了提高系统速度的瓶颈。在设计中对系统传输由于是用DMA和Mcbsp的结合使用,速度超出了其他程序的执行速度,只要传输在主函数的执行时间内完成就不会造成系统的阻塞,所以这部分只测试和评估各程序的执行速度,传输的时钟定位脉冲是对CPU时钟的35分频远远快于处理速度,忽略它的测试不会对整个测试有很大影响。

系统数据的传输速度达到100kbit/s,传输只要在上次数据处理完前完成就可以不计算传输的速度,所以按照我们的预期速度,和我们DSP的CPU时钟140MHz,可以算出所有的数据要在多少条指令周期内完成才不会对下一阶段的任务产生影响,而CCS就有专门的测试工具帮助我们测试执行的指令周期。期望的最大执行周期为140÷125×64=71680条指令周期。

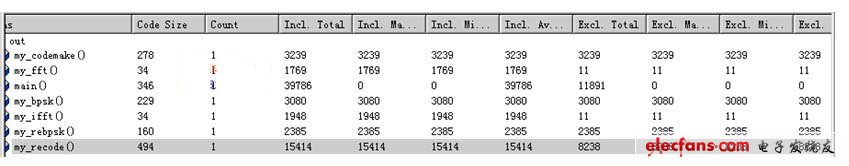

由CCS自带的时间测试是以执行周期为单位的,在程序没有进行编译优化时,我们测试得各部分和主函数的执行速度如图2所示:

图2 未优化前的程序执行时间测试结果

在此结果中,我们可以看到

- OFDM技术在应急通信系统中的应用(08-28)

- OFDM技术简介(10-11)

- OFDM应用中的关键技术解析(10-11)

- OFDM系统仿真与分析(10-11)

- 基于PLC和OFDM技术的电力线载波技术在工厂数据传输中的应用(03-02)

- 压缩感知技术在未来移动通信系统中的应用(08-05)