高速信号仿真在定位接收机设计中的应用

1 引言

高灵敏度卫星定位接收机主要由天线、射频模块、基带模块、pvt解算模块与通信及应用模块组成。如图1所示。

图1 接收机结构框图

卫星信号(中心频率为gps、galileo l1波段1575.42mhz)通过天线(包括低噪放)和射频模块接收。其中射频模块将内部16.368mhz的高精度tcxo时钟经过锁相环96倍频后将l1波段信号下变频为4.092mhz模拟信号,并由该16.368mhz时钟采样,最后将4.092mhz的2位数字中频信号传给fpga模块。为确保定位解算时间同步,同时将16.368mhz的时钟作为fpga平台的输入时钟。

基带模块fpga平台将时钟信号和数字信号进行相关运算处理,然后通过高速总线方式传输给pvt解算模块进行位置解算,高速总线频率为66mhz。

由于上述信号频率较高且作为高灵敏度接收机,接收灵敏度需达到-144dbm。后端通信及应用模块通过无线通信方式收到参考接收机的卫星星历等信息数据并将该信息通过串口传输给pvt解算模块,大大提高接收机的捕获灵敏度。高速的信号如果完整性没有处理好,将直接干扰前端射频信号,从而大大影响整个接收机的性能。在硬件设计中重点考虑基带部分高速信号传输线的反射和串扰效应,并通过pcb板的叠层设置和控制pcb线宽线距来解决产生的影响。

2 传输线理论分析

2.1 传输线阻抗

传输线用于将信号从一端传输到另一端。所有传输线都是由两条一定长度的导线组成,其中一条为信号路径,另一条为返回路径。高速数字电路中传输线效应主要表现为数字信号的过冲、下冲和振铃现象。这些现象不仅会使数字信号传输发生错误,严重的情况还可能破坏部分芯片和降低其他功能模块的性能。这三种现象产生的根本原因是由于信号沿互连线传播时受到的瞬态阻抗发生变化。该类变化的大小可以用反射系数来说明。

反射系数式(2-1)

z1表示信号最初所在区域的瞬态阻抗,z2表示信号进入区域的瞬态阻抗。由式(2-1)可知当瞬态阻抗相同时,反射系数为0;瞬态阻抗差异越大,反射信号就越大。由此可见,在pcb设计时只要控制好整板的传输线(即重要高速信号走线)的阻抗,就能使信号反射尽可能地减小。

2.2 传输线串扰

串扰指有害信号从一个网络转移到相邻网络。在pcb板中,我们通常把数据总线或者地址总线平行的点对点布线。当这些总线从逻辑高到低电平切换时会产生串扰。通过叠加分析,串扰所产生的噪声超过信号电压摆幅的15%时,就会影响整个系统的稳定性。所以对于总线上其中一条线对另一条静态线之间的可容许耦合噪声的分析将变的及其重要。边缘场是引起串扰的根本原因。减小串扰的最主要途径就是使网络间的距离足够远,这样可以把它们之间的边缘场减小到可接受的水平。因此,在pcb设计时,总线的布线在结构允许的范围内将线宽加大可以较显著的减小传输线的串扰。

3 pcb板设计

3.1 电源、地平面分析和叠层分析

电路板的地平面和叠层设计将直接影响整个板子的性能。高速信号电流总是沿着最小电感路径前进,返回信号电流趋向于信号导体的附近,电流密度随着其相互距离增加的平方而下降,因此地平面和叠层设计将会大大改善信号的串扰。考虑整板采用10层板设计,具体设计和设置如图2所示。对于电源层和地线层,全板的主电源为3.3v和1.2v,其中还有5v数字电源、3.3v模拟电源和2.5v的数字电源。

3.3v为单独一层电源,另一电源层分割成1.2v和5v两块。3.3v模拟电源和2.5v数字电源通过走线层来完成。

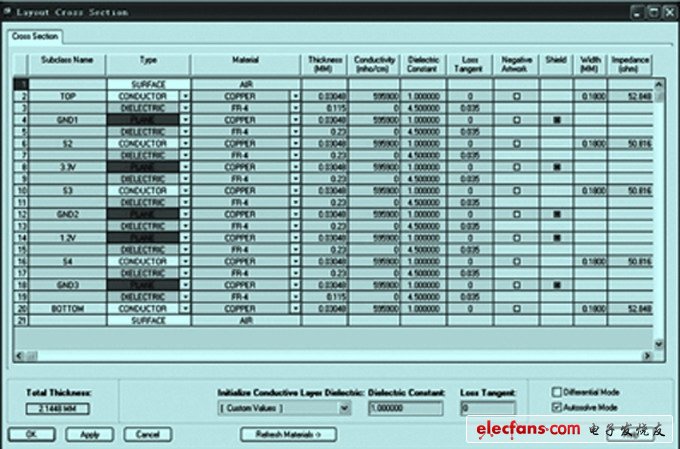

图2 pcb板叠层及走线阻抗匹配设置图

3.2 信号走线设置分析

信号层考虑阻抗匹配,选用单线阻抗为50ω,差分线阻抗为100ω。通过candence allegro pcb si gxl软件的layout cross secTIon来设计。考虑到机械尺寸匹配和物理承重等因素,整板厚度设计为2.1mm,并成对安排平面。该软件能够根据设置fr4介质和铜箔的厚度,确定单线50ω阻抗和差分线100ω阻抗的各层走线宽度。

4 建模仿真

在确定完地平面和叠层后,就可以进行建模和仿真。对于一个复杂的系统来说,对所有的信号进行仿真是不可能也是做不到的。提高系统性能的关键在于对某些特殊信号的仿真,做到在制板前能够定量的了解和改善这些信号状况,从而提高整个系统的性能。

接收机中的fpga采用片外sdram存储,时钟频率为100mhz。sdram模块的时钟线、地址线和数据线必须做仿真。由于数字总线采用64位宽,因此选用4片16bit的sdram芯片。

首先通过网上下载fpga straTIx2和sdram pc256_sdr的ibis文件库,将芯片资料导入工具后建立的模型如图3所示。其中u35为

- 硬件工程师谈高速PCB信号走线规则TOP9(03-26)

- LT3751如何使高压电容器充电变得简单(08-12)

- 三路输出LED驱动器可驱动共阳极LED串(08-17)

- 浪涌抑制器IC简化了危险环境中电子设备的本质安全势垒设计(08-19)

- 严酷的汽车环境要求高性能电源转换(08-17)

- 适用于工业能源采集的技术 (08-10)