Xilinx最新射频级模拟技术,实现面向5G无线的颠覆性技术突破

新型RFSoC 能将功耗和封装尺寸减少50-75%,

对高效部署5G 大规模MIMO 和毫米波无线回传至关重要。

简介

随着通信行业逐渐向5G 标准靠拢,移动设备制造商十分钟情于技术试验和概念验证测试。现在,这些技术的商业可行性正在进行严格评估,然而原型设计所使用的很多技术都无法很好地转化为商业部署。

由于目标是以更低功耗通过频谱效率、高度致密化以及新频谱来提高网络容量,因此制造商正在依靠软件、硬件和系统级的技术突破来实现目标。

有些技术对满足严苛的网络容量目标具有至关重要的作用,而大规模多输入多输出(MIMO)天线阵列就属于这类技术。与这些天线阵列进行接口连接的射频单元必须满足极其严格的功耗和封装尺寸要求,但如果没有系统集成方面的突破,这些目标很可能无法实现。

赛灵思不断在准5G 和5G 技术的实现、试验和商业化中扮演主要角色,促进网络设计中的灵活性和可编程性。

为使大规模MIMO 系统的商业化成为现实,赛灵思正推出首款采用RF 级模拟技术的全可编程(All Programmable)RFSoC,该方案在集成方面取得了突破性的进展,其将高性能ADC 和DAC 完美集成到了SoC 中。通过用集成直接RF 采样技术取代分立数据转换器,RFSoC 可削减50-75% 的功耗和封装尺寸,这也是大规模MIMO 5G 无线电和毫米波无线回传的关键。同时,SoC 与直接RF 信号处理的结合为数字域中提供了全面的灵活性,将我们与适合商用、面向无线基础设施的软件无线电的距离拉得更近了。

功耗与封装尺寸 –5G 商业部署的关键

传统4G 射频接入网络(RAN)通过高损耗的同轴电缆与远端射频单元建立有线连接。尽管远端射频架构是从3G 演进而来,但该方案仍存在一些问题。从天线到远端射频单元的功耗依然非常大,而且系统体积大,无法实现密集部署。

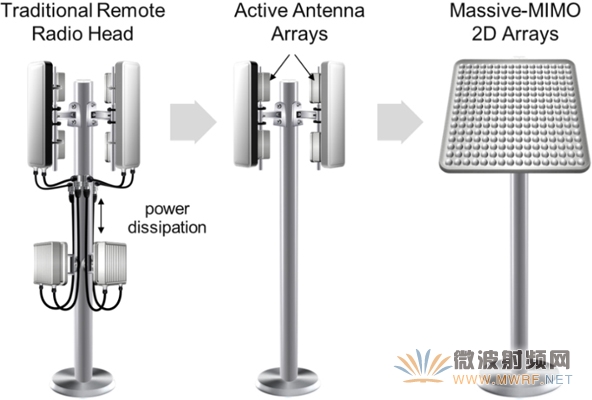

如图1所示,RAN 演变过程中的下一步是使用有源天线阵列(使数字和模拟射频单元与天线的距离更近),以节省空间,避免电缆损耗和相关功耗,同时改善链路预算。有源天线阵列在4G 很成功,但是无法满足5G 连接设备数量和用户数据速率的提高。

图1:远端射频设备和天线系统的演进

大规模MIMO 和波束成型技术占解决方案中的很大一部分。根据图1所示,"大规模"MIMO 配置可将32、256 甚至多达1024 个独立[物理] 天线整合到一个2D 阵列中。它们的相控阵列特性能实现高分辨率波控和更低功耗,允许进行非常高密度的安装,显著提高每单元容量。有了这种2D 阵列结构,就可以在非传统布局中使用新型网络拓扑结构,包括以"瓦片"形式安装到建筑物侧面,或采用不规则形状的广告板或名牌。

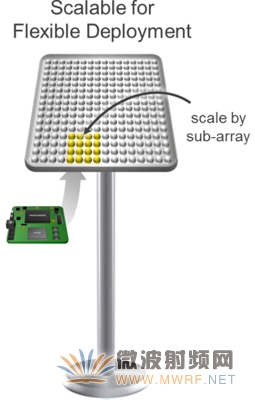

为了支持这些大规模MIMO 阵列,远端射频单元需要紧凑性,并且能够支持子阵列以实现灵活和可扩展的天线配置。

图 2:通过子系统可扩展性实现灵活开发

业界首款AllProgrammable RFSoC

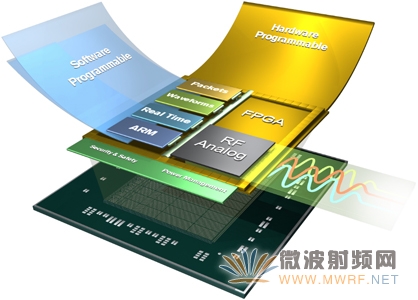

AllProgrammable RFSoC 能解决上述所有这些问题。该器件将通信级RF 采样数据转换器(配有数字处理子系统)、稳定可靠的ARM 级处理系统以及FPGA 架构整合到单芯片器件中。从而在集成度方面取得了重大突破。尤其是模拟到数字信号链得到硬化DSP 子系统的支持,便于模拟设计人员进行灵活配置。这样可将系统功耗和系统尺寸降低50-75%,并达到所需的灵活性以适应不断演进的规范和网络拓扑结构。

图3:推出首款All Programmable RFSoC

减少功耗、封装尺寸和设计周期

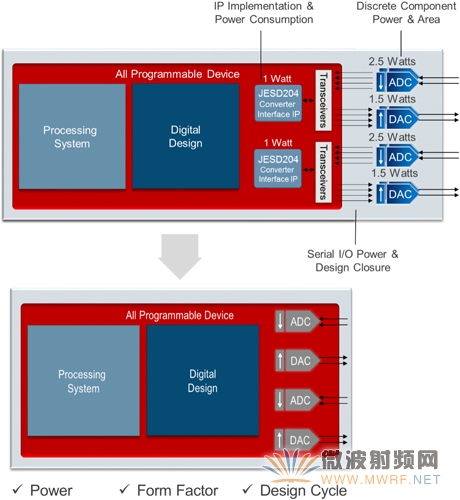

传统的无线电系统包含一个处理器、可配置逻辑、连接IP,当然还有数据转换器。当在高RF 频率下工作时,典型的单通道ADC 的功耗约为2W,DAC 的功耗约1.25W。通过集成减少组件之后,能降低功耗和封装尺寸,这对于高通道数的系统来说效果显著。除了这些优势以外,集成还能明显简化系统设计。

主要原因在于,与大量分立式转换器建立连接将面临很大的I/O 挑战。为了随带宽扩展,大多数新型转换器都使用基于JESD204B 协议的速率高达12.5Gb/s 的高速串行接口。这种方案存在很多问题。首先,JESD204B IP 核的实现需要时间,要使用宝贵的FPGA 架构,并消耗大量的功耗。其次,串行I/O 功耗在更高数据速率下会显著增加。不过,最难的还是建立串行链路。12.5Gb/s 速度下的信号失真是个问题,大多是通过高损耗低成本铜缆连接运行高线路速率所致。这个过程令人不爽,模拟设计人员迫切希望解决。

图4:通过集成来减小功耗、封装尺寸和设计周期

集成转换器之后就无需再使用JESD204B IP 核和串行收发器。其优势不局限于减少功耗和封装尺寸,还能大大缩短开发时间。

功耗降低达50%

从初步测量结果来看,功耗削减效果明显。在典型4 路发送、4 路接收(4Tx/4Rx)天线

- 众不同的WiMAX产品(07-08)

- 全球主要射频芯片器件厂商(10-06)

- 天线及射频无源器件互调指标测量技术方案(02-12)

- RF电路设计中的常见问题(06-14)

- 数字接收机中ADC和射频器件的动态性能要求(06-12)

- 中国工程师标配十款经典RF射频器件(06-18)