PCI Express 4.0通路裕量和其优点分析

当面临更高带宽和更快上市时间的要求时,设计人员将面临新的挑战。较高的数据传输速率使得更高带宽成为可能,同时它们会限制传输距离(由于信道损失增大),使信号的完整性降级,并降低制造良率。解决这些挑战需要时间和资源,这会对系统设计进度造成负面影响,更糟糕的是,在设计系统时,这类负面影响可能并不明显。

通过在接收器处引入PCI Express 4.0(PCIe 4.0)通路裕量特性,PCI-SIG正在解决该项挑战,通过引入该项特性,系统设计人员能够评估其系统的性能变化容差。通路裕量允许系统设计人员使用PCIe 4.0装置来测量每一系统中的可用电气裕量。在本文中,介绍了通路裕量特性,以及它是如何使设计人员按时交付更健壮系统的。

系统中的性能变化

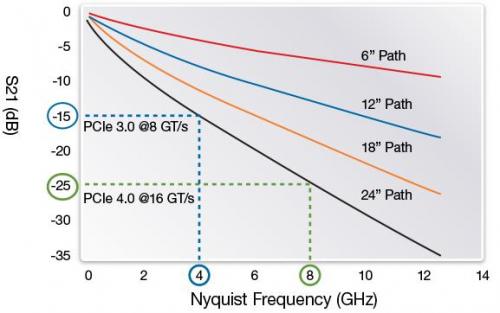

PCI Express是一种点对点互连,它支持内部和外部连通性,或是通过线缆进行,板级连接。有三种常见的板级连接情形,它们是芯片对芯片(无连接器)、单个板和连接器的扩展卡接口、以及带多个板和连接器的背板。在复杂的背板情形下,很多原因都可能会导致信号完整性降级,包括串扰、反射、不连续和信道损失。在图1中,给出了一个在FR-4印刷电路板(PCB)上的信道损失差异示例,其中,与8 GT/s PCIe 3.0相比,24英寸走线在16 GT/s PCIe 4.0下具有更高的损失。

图1:6"/12"/18"/24" FR-4 6mil条线PCB上的插入损失

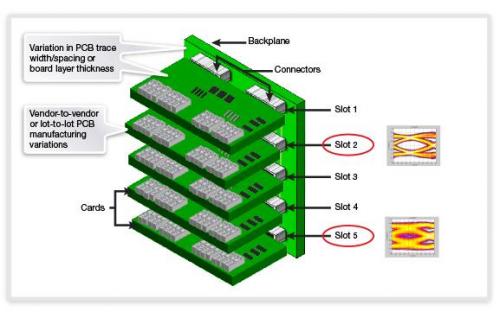

由于PCB和连接器制造方面的差异,对于某一插槽中的某一卡,与运行在另一插槽上的采用不同制造的另一卡相比,会具有不同的信号性能,如图2所示。由于PCB制造变化,如板层厚度、走线宽度或走线间距,都会增大信道损失、阻抗和系统噪音。对于它们中的任一个或全部,会影响信号眼图的质量和打开尺寸。在不同厂家或来自同一制造商的不同批次之间,可看到这类PCB差异。

图2:在背板系统中造成性能变化的影响因素

环境变量也会影响系统中的信号性能,如温度和湿度,PCB和连接器特性变化会影响实际信道损失和信号完整性。

在更高的数据率下,制造和环境变化的影响会放大。因此,在发布之前,设计人员必须仔细评估高速系统的工作安全系数,避免在最后一分钟进行系统优化,这会延迟推向市场的时间。在构建最终系统之前,进行建模和模拟相当复杂、耗时且成本昂贵。为了避免这些问题,系统设计人员需要使用有效且经济的方法来执行裕度分析。

使用通道极限来克服性能变化问题

对于所有的PCIe 4.0端口,接收器处的通路裕量是一种强制特性,其中,PCIe控制器从PHY接收器处获取裕量信息,同时工作在数据率为16GT/s的主动模式下(L0链路状态),不需要任何额外的外部硬件。使用通道裕度控制和错误通报特性,通过评估接收器的眼宽(时间)和眼高(信号幅度,电压),控制器能够确定系统中每一PCIe通道的裕量。这样,就能有效评估PCIE装置处的系统裕量,无需任何额外设置。

对于在PHY和控制器中实际实施的裕量特性,它与具体设计相关。在某些设计中,利用PHY中的数据和错误样本来评估信号眼图通报的信息,在其他设计中,可能会选择简单地通过将恰当的抖动量注入到数据中来对眼图进行加扰。对于由PHY提供的数据,控制器可能会以不同方式对这类数据进行裕量评估。对于不同级别的数据采集粒度,控制器可能会使用不同的偏差、电压和定时步骤。此外,在退出裕量评估之前,可能会设置不同的位容错限度。

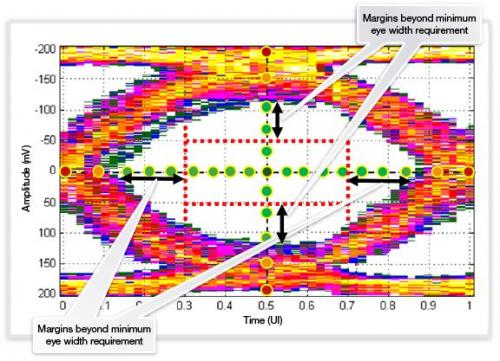

在图3给出的示例中,对于错误扫描,通过在PHY中移动数据或错误样本的位置,可实现通路裕量。从接收器眼的样本位置开始,按增量步进,向左向右扫描眼宽,检查最低眼宽裕量。作为可选方式,能够从样本位置开始向上向下扫描眼高,检查最低眼高裕量。控制器使用来自PHY的裕量信息,识别系统中故障发生的位置,并确定通道裕量。图3给出了16GT/s PCIe 4.0处的接收器眼示例,它处于最佳位置,具有较大的信号裕量,超出最低眼宽和眼高。

图3:PCIe 4.0接收器信号眼示例

总结

当数据率从PCIe 3.0s 8GT/s翻倍到PCIe 4.0s 16GT/s时,性能变化和信号完整性降低变得更加显著。此外,PCB制造和环境变化也会增大信道损失,串扰和信道不连续,从而导致系统噪音增大、抖动性能变差和信号眼关闭。使用即将到来的PCI Express 4.0规范中提供的通路裕量特性,通过获取裕量信息,借助PCIe 4.0 PHY和控制器解决方案,能够帮助系统设计人员在设计和生产周期早期评估其设计的性能变化容差。这样,系统设计人员就能交付更健壮的系统,更好地满足其尽早推向市场的目标。

Synopsys的DesignWare PHY和控制器IP解决方案针对PCI Express 4.0技术,支持具有

Synopsys PCI Express 4 0 相关文章:

- 如何快速解决隔离FPGA设计中的错误(08-26)

- SoC系统开发人员:FinFET对你来说意味着什么?(11-12)

- PCI Express交换及桥接芯片的设计(10-21)

- 电池充电器电路PCB设计(05-24)

- IBIS模型:利用IBIS模型研究信号完整性问题(09-08)