精确估算SoC设计动态功率的新方法

通过省去基于文件的流程,新工具可提供完整的 RTL 功率探测和精确的门级功率分析流程。

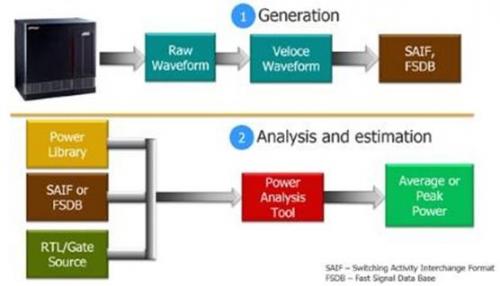

在最近发布的一篇文章中,笔者强调了当前动态功耗估算方法的内在局限性。简单来说,当前的方法是一个基于文件的流程,其中包括两个步骤。第一步,软件模拟器或硬件仿真器会在一个交换格式 (SAIF) 文件中跟踪并累积整个运行过程中的翻转活动,或在快速信号数据库 (FSDB) 文件中按周期记录每个信号的翻转活动。第二步,使用一个馈入 SAIF 文件的功率估算工具计算整个电路的平均功耗,或使用 FSDB 文件计算设计时间和空间内的峰值功率(见图 1)。

图 1. 传统的功率分析根植于基于文件的两步法。

当被测设计 (DUT) 相对较小(约数百万门或更少),且分析周期较短(不超过百万个时钟周期),这些方法可能行得通。上述时间窗口常见于自适应性功能验证环境。

然而,如今的大型 SoC 设计具有数千万或数亿个门来执行嵌入式软件(比如,启动一个操作系统或运行需要数十亿个周期的应用程序),若使用传统方法就会面临以下三大难题:

1. SAIF 文件将变得太过庞大而无法管理,FSDB 文件则更是如此。

2. 文件生成过程慢如蜗牛,短则数小时,长则超过 1 天。

文件加载到功率估算工具的速度也相当缓慢,少则几天,多则超过 1 周。

这一切似乎注定了无法成功。

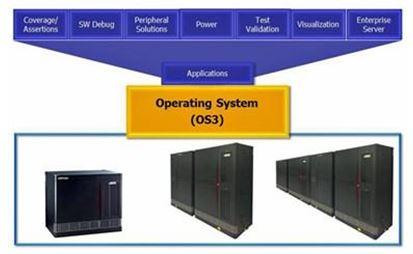

这一状况随着 Mentor Graphics 在 2015 年 5 月 27 日发布 Veloce 功耗应用程序而发生了改变,这款软件包带有 Veloce 活动图和 Dynamic Read Waveform 应用程序编程接口 (API),接口位于 Veloce OS3 顶部(见图 2)。

图 2. 操作系统可保护任何应用程序不受下层硬件仿真器的干扰。

Veloce 功耗应用程序解决了影响传统(且有争议)的功耗评估算法速度的一些核心问题。它通过将 Veloce 硬件仿真器紧密集成到功率分析工具中而省去了基于文件的两步流程。

设计团队无需再处理巨大的文件。这意味着,再也没有空间浪费,文件创建和文件加载也将节省大量时间。新方法能够快速、简洁、高效且全面地估算现代 SoC 设计的功耗。

Veloce 活动图

Veloce 活动图在一个简单的图表中映射出了全局设计切换活动随时间的动态变化,例如,在启动 OS 和/或运行动态应用程序时(见图 3)。

图 3. Veloce 活动图在长时运行中识别焦点区域。

活动图可识别高频切换活动的时间帧,高频切换活动可能给设计团队带来功耗问题。尽管此图表并不独特,但其生成所需的时间要比基于文件的功耗图表快一个数量级。作为一个数据点,对于一个 1 亿门设计、7500 万设计时钟周期的活动图,Veloce 需花费 15 分钟来生成。相比之下,功率分析工具则需要花费超过 1 周的时间来生成类似信息。况且,它们可能还无法处理如此巨量的数据。

随之而来的问题则是:这些峰值出现于 DUT 中的"何处"以及是由"什么"引起的?这可通过 Dynamic Read Waveform API 来回答。

Dynamic Read Waveform API 流程

一旦高频切换活动的时间帧在设计的顶层被识别,设计团队就能放大这些时间帧。用户能够深入到设计的层次结构和嵌入式软件中,从而找到产生此类高频切换活动的根源。为此,用户可以使用 Dynamic Read Waveform API。

Dynamic Read Waveform API 可通过将硬件仿真器中的切换数据实时传送入功率分析工具中,从而取代繁琐的 SAIF/FSDB 文件生成过程。从硬件仿真 SoC,到输入切换数据,再到使用功率分析工具读取切换数据,以及生成对应的功率值,所有操作都是同时运行的。其实际效果是整体性能的飞跃,而这正是启动操作系统和运行真正的应用程序所需要的(见图 4)。

图 4. Veloce 电源应用程序可加快 Veloce 功耗分析速度,让设计团队在执行生成、分析和估算时一步到位。

作为附加好处,与基于 SAIF 的普通流程相比,Dynamic Read Waveform API 的精度更高,因此可对各内存和 IP 块进行精确的功耗估算。

最关键的一点在于,Dynamic Read Waveform API 支持通过基于软件的测试在系统级进行功耗分析与功耗探测,如果采用基于文件的流程,这几乎是不可能的。

结论

Veloce 功耗应用程序推动了功率估算方法的转变。Dynamic Read Waveform API 与功率分析工具的独特整合,省去了基于文件的流程,可提供完整的 RTL 功耗分析和精确的门级功率分析流程。

这意味着,设计和验证团队能够在设计周期内及早开始 RTL 功率分析。与以往相比,他们可以更早地执行功率权衡和架构调整。此外,在 RTL 合成为门级表示后,他们可以继续使用之前的流程。在门级,他

SoC 动态功率 动态功耗 RTL Veloce 相关文章:

- SoC系统开发人员:FinFET对你来说意味着什么?(11-12)

- SoC内ADC子系统集成验证挑战(01-16)

- 不可不知的几种真实设计环境中的系统设计(01-21)

- 引入EDA技术进行数字电路设计的方案(05-25)

- PCB设计:如何减少错误并提高效率(01-23)

- 网络产品上市时间怎样缩短?这要看硬件仿真器的!(09-08)