FPGA验证技术在航空电子领域的应用

技术产生背景

随着航空电子系统复杂性的增加,以及增加使用现场可编程门阵列(FPGA)的硬件验证是航空航天领域内的一个主要问题。事实上,除了承认使用常用的电子设计自动化(EDA)工具- 设计输入,综合,布局布线,静态时序分析- 美国联邦航空管理局(FAA)的官员在欣赏EDA工具如何能够提高验证,可追溯性和项目管理。值得庆幸的是,在更广泛的半导体行业正在使用的工程师航空电子设备应用程序可以在一定的方法绘制基于FPGA的设计工作,以验证应用专用集成电路(ASIC)设计。

尽管它们具有不同的商业模式,其体积是一个关键的区别中,航空电子设备公司的FPGA和一个半导体公司设计的ASIC可以使用许多相同的硬件验证技术设计- 其条件是在航空电子公司还必须通过严格的认证流程,通过正式RTCA / DO-254("设计保证指南机载电子硬件")。

该DO-254标准规定的硬件设计和硬件验证应该是独立的。在设计的生命周期而言,这意味着设计工作,以满足规定的要求和验证工程师寻求证明该设计符合要求(即基于需求的验证或RBV)。

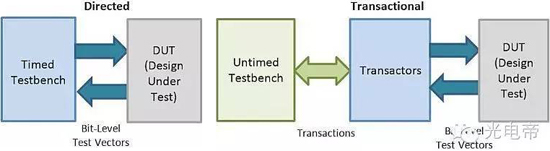

现代的,尤其是自动化,可使用验证技术的航空电子设备的设计的验证,但可能不适合用于认证目的。例如,基于事务的验证(TBV),其广泛用于更广泛的半导体工业中,以高级别要求操作,但可能不适合的低级别的要求,如单个信号的定时的验证。然而,这并不是说TBV没有发挥作用,航空电子设备的设计在未来发挥,现在越来越多等等。航空电子系统的复杂性不断增加将推动朝RBV TBV,很可能是通过要求的方式被表达更有利于TBV。

为什么单独模拟是不够的

模拟器起到验证了巨大的作用。 (使用不同的模拟器),因此,以执行不同的模拟的需要- 虽然非常有用的,它们是,在一定程度上,在相当有限的工具它们只能提供在设计流程中的某些点的设计的信心。

例如,一个HDL仿真验证设计(作为编码在VHDL中,例如)的行为如预期。它通过行使使用HDL测试代码的综合RTL子集(即,在寄存器传输级设计意图)做到这一点。模拟器是完全确定的,因为它总是会产生对给定的设计和测试平台相同的结果。然而,真正的硬件不确定性。多个时钟域,例如,引入不确定性。此外,RTL仿真与理想的时钟进行,时间不一致而像亚稳态效应不蓝本- 也不是时钟相位和频率漂移。

时序仿真是因为时间的不成比例需要模拟甚至几秒钟的价值FPGA操作的更准确,但很少实用。幸运的是,RTL模拟可以增强引进在模拟跨时钟域路径的不确定性的建模。

值得注意的是,在更广泛的半导体行业,一些ASIC验证团队声称,HDL仿真器不使用在所有的验证环境中。此外,对于非常大的设计,丰富的RTL模拟可能不会因为所花费的时间逼真。相反,仿真器被用来加快验证过程。

仿真器使用多个FPGA来实现设计。通过将硬件在环,信心增加;但不一定为100%,作为仿真设计可能是也可能不是确定的,可以或可以不能够模拟现实亚稳态的问题和非理想的时钟。这一切都取决于仿真的设计是如何映射到仿真器的FPGA以及如何生成的时钟。

它是可以观察到真实的硬件(即,FPGA)的同时运行的仿真,提供该ASIC测试设计用于非确定性的行为制备的行为。此外,它们不得包含任何假设,如从测试响应总是出现一个给定接口上在给定的时间。这是因为,在实际硬件中,响应可以更早或更晚出现- 甚至可能被重新排序- 由于仿真设计的不确定性的行为。

这是很容易实现的"定向"这样的假设和定时测试平台,其中仅在模拟运行,而半导体公司使用不定时的"交易"测试平台(见图1),其中涉及到时间的任何假设的实现都很难实现。经过测试的设计要求通信接口协议封装在交易者。只有交易者可能包含定时HDL代码,通常由接口协议要求。

原理解析

原理如图所示

图1:导演和交易测试平台

在硬件验证的好处

可以理解,验证在环硬件带来了更多的现实验证过程。然而,对于一个基于FPGA的航空电子设备的应用程序,这将是矫枉过正映射FPGA设计到基于多片FPGA仿真器。

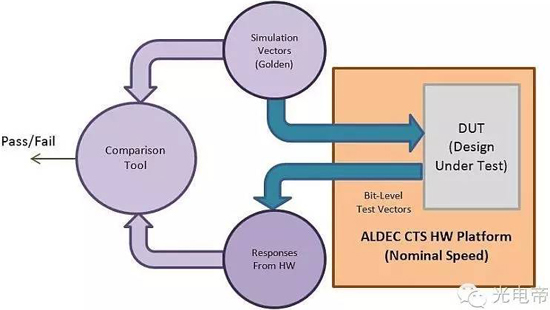

这是很容易采取目标FPGA及其接口连接到验证环境。许多航空电子设计,例如,使用Aldec公司的DO-254符合性测试系统(CTS)(见图2),不仅验证他们的设计,而且还根据RTCA / DO-254规范,以取得所需认证学分。

图2:Aldec公司的DO-254/ CTS平台- 用于'在速度,在硬件'验证

在CTS中,目标设计运行在目标设备在高速(其被安装在一个自定义的子板)。仿真测试平台作为测试向量,以支持100%的FPGA引脚级的可控性和可见性需要测试RBV实现正常范围和异常范围的测试。

这里的问题是:能否传统执导测试平台,航空电子行业内流行的,适

FPGA 相关文章:

- MIMO 系统的快速原型设计与验证(04-28)

- 基于FPGA的多按键状态识别系统设计(08-15)

- ARM、DSP、FPGA的技术特点和区别(01-22)

- 3G移动通信中脉冲成形FIR滤波器的ASIC实现结构(01-24)

- 应用EDA仿真技术解决FPGA设计开发中故障的方法 (03-01)

- 基于FPGA的IRIG-B编码器实现(02-19)