如何选择满足FPGA设计需求的工艺?

FPGA在系统中表现出的特性是由芯片制造的半导体工艺决定的,当然它们之间的关系比较复杂。过去,在每一节点会改进工艺的各个方面,每一新器件的最佳工艺选择是尺寸最小的最新工艺。现在,情况已不再如此。

取而代之的是,当今的可编程逻辑供应商必须研究各种工艺选择,才能满足采用FPGA的设计的各类需求。本文将介绍三类工艺特性,它们与现代FPGA内部结构的联系,以及FPGA对采用了这些工艺的系统的影响。其中将特别介绍围绕名为FinFET的晶体管加速应用的革命性变革,Altera怎样采用独特的FinFET工艺,特别是Intel的14nm三栅极工艺进一步提高FPGA密度、性能和功效,而这是平面FET技术发展根本无法实现的。

工艺特性

对于IC设计人员,有三类由工艺决定的特性,这些特性一起体现了工艺。它们是特征层距、晶体管行为和可用性。

层距是指成品IC类似特性之间的最小间隔,有助于确定管芯尺寸和容量,还能够间接地决定电路速率和功耗。管芯的每一特征层--晶体管、本地互联、接触,以及连续的上面金属层,都有自己的层距。由工艺工程师根据光刻极限和其他工艺约束、成本以及工艺设计人员认为客户会怎样使用工艺来选择这些不同层的间距。这些层距相互作用,决定了某一类电路中晶体管的实际密度。

让我们从底层开始。在某一电路中封装多少晶体管大致取决于两个问题:晶体管能够靠得多近,互联之间有多大的间距才能满足它们的连接要求。两者都会带来限制,这取决于电路设计和布局。当然,晶体管能够封装的距离有多近取决于其大小和形状。

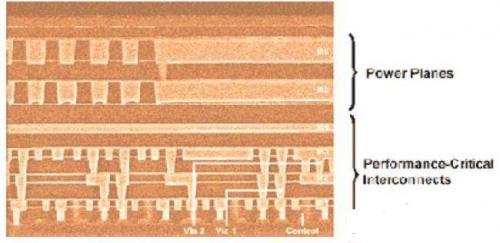

从本地互联、接触层往上,越到上面的金属层堆叠(图1),层距就越会急剧增大。一般而言,本地互联和下面金属层连接附近的晶体管,决定了标准单元或者SRAM等仔细封装的结构的密度。上面的金属层连接电路,最终将功能模块连接起来,实现总线连线,分配电源和时钟连接。上层的数量和层距对于芯片设计人员而言也非常重要,这是因为它们决定了芯片不同部分之间连接的带宽和功耗。

图1.堆叠越高,金属层距越大,如这一传统的Altera CPLD所示。

晶体管特性

最简单的情况是,数字设计人员对于其晶体管只关心三方面:它们有多大、晶体管开关能有多快、它们的功耗有多大。多年来,这三方面互相协调发展的非常好:每一新工艺节点的晶体管尺寸都在减小,开关更快,功耗更低。

但在最近的工艺代,随着晶体管尺寸的减小,功耗分成了两个不同的部分:由开关活动造成的动态功耗,以及晶体管无法关断的电流所消耗的泄漏功耗。速度和动态功耗一直是相关的,在每一新工艺节点,速度逐渐提高,开关功耗慢慢下降,而静态功耗在每一新节点都在增大。现在,如果希望晶体管非常快地进行开关,那么,它会泄漏。如果希望降低泄漏电流,晶体管的速度就会变慢。相应地在芯片级,某些28nm SoC,一半的功耗都是静态泄漏功耗。

工艺和电路设计人员对此进行了反击。工艺工程师为芯片设计人员提供了具有不同速度和泄漏电流的各类晶体管。电路设计人员仔细地选择了晶体管,考虑了它们的关断时钟能力和供电电压,以便有效的管理功耗。这些创新使得设计人员能够开发基于单元的数字模块,同时具有较好的峰值性能和较低的泄漏。

但是,平面FET的问题却越来越严重。在以后的工艺代中,越来越难以进一步降低平面FET的工作电压。今天,很多工艺工程师同意,在20nm节点以后,再也不可能降低平面FET的延时功耗:电路设计人员围绕这一指标来综合考虑速度和功耗。虽然已经尽最大努力来延长传统平面FET的生命周期,但是,它还是在逐渐淡出。

今天,很多工艺设计人员相信,未来属于一类新晶体管:FinFET,即Intel把他们的这类器件称之为三栅极晶体管。实际上,晶体管是竖立在其侧面的,在其他三个裸露侧封装栅极,FinFET的栅极能够更好地控制通过沟道的电流,与同样大小的平面FET相比,在速度一定时,显著降低了泄漏(技术上,更低的阈值电压)。更低的泄漏使得设计人员能够以较低的电压实现要求的工作频率,同时降低了动态和泄漏功耗,或者在一定的总功耗水平上,以更高的速度工作。

而且,由于晶体管是竖立在其侧面上,影响驱动电流的沟道宽度不会直接限制晶体管彼此之间封装的距离。因此,FinFET阵列要比使用相同沟道宽度的平面FET阵列的密度高得多。而且,由于器件的尺寸,FinFET原理上要比最小尺寸的平面FET的一致性更好。工艺工程师解释说,平面器件在理论上已经变得非常小,以至于可以数出沟道中掺杂原子的数量。不管出于什么原因,在生产过程中一些原子出错是难以控制的,这会导致晶体管阈值电压有很大的不同,因此,其电气性能也会不同。FinFET对这类变化的敏感度要低得多。

FinFET在几方面显示出完全不会有平面FET那样越来越多的问题。FinFET可以封装得更靠近一些。它们有更低、一致性更好的阈值电压,不会出现不可接受的泄漏电流。较低的阈值电压支持工作在较低的供电电压下,显著降低了功耗,或者工作在正常电压下,但是大幅度提高了速度。

- EDA技术的概念及范畴(11-12)

- 实时签核反馈在AMS设计中的价值(03-25)

- 基于FPGA的空间电场信号采集系统设计(11-28)

- Cadence 推出创新的FPGA-PCB协同设计解决方案(04-25)

- 小工具蕴藏大智慧,WEBENCH让设计更轻松(05-20)

- 如何快速解决隔离FPGA设计中的错误(08-26)